西安邮电大学:《数字电路与逻辑设计》课程教学资源(试卷习题)2008数字电路与逻辑设计C卷(试题)

共5页第1页 西安邮电学院课程考试试题(卷) 2008 -一2009学年第一学期试题卷 课程名称:数字电路与逻辑设计 试卷类型:(ABC)C卷专业、年级:通工/电子科技/光信息06级 题号 二 三 四 五六七八九 总分 得分 、填空(10分)》 1、F=AB+C+A,则F的反函数(用反演规则)下= F的对偶式F= ,F的标准与或式为 2、(30.25)10=( )16=( )8421BD码 =( )余380码 3✉ 一个模值32的递加计数器的初始状态为00000,经过48个CP脉冲后,其状 态为 4、 容量为16KX16位RAM的地址线有根,数据线有根,用其构成容量 为32KX16位的RAM需要进行扩展。 二、选择(20分) 注意:题中涉及到的中规模器件的功能表,附在试题的最后一页 将正确答案填入下面答题栏中,所选的答案用横线划过,例如:由 题 2 345678910 ¥ BBBBBBBBBB D DD DD DD DD 说明:1。拟题请用碳塑最水钢笔书写。不要出框。除填空体、图解及特要求外一般不留答题空间

共 5 页 第 1 页 说明:1。 拟 题请用 碳塑 墨水钢 笔书写 。 不 要 出 框。 除 填 空体、 图解 及特要 求外 一般不 留答题 空间 。 - - 上- 装- 订- 线- 专业班级 姓名 学号(8 位) 西安邮电学院试题卷专用纸 - - 密- 封- 装- 订- 线- 西安邮电学院课程考试试题(卷) 2008-2009 学年第 一 学期试题卷 课程名称:数字电路与逻辑设计 试卷类型:(A B C)C 卷 专业、年级:通工/电子/科技/光信息 06 级 题号 一 二 三 四 五 六 七 八 九 总分 得分 阅 卷 人 一、填空(10 分) 1、 F = AB + C + A ,则 F 的反函数(用反演规则) F =_ _, F 的对偶式 * F =_ ,F 的标准与或式为: _。 2、 (30.25)10 = ( )16 = ( )8421BCD 码 = ( )余 3BCD 码 3、 一个模值 32 的递加计数器的初始状态为 00000,经过 48 个 CP 脉冲后,其状 态为_。 4、 容量为 16K×16 位 RAM 的地址线有 根,数据线有 根,用其构成容量 为 32K×16 位的 RAM 需要进行 扩展。 二、选择(20 分) 注意:题中涉及到的中规模器件的功能表,附在试题的最后一页。 将正确答案填入下面答题栏中,所选的答案用横线划过,例如: 题 号 1 2 3 4 5 6 7 8 9 10 选 择 答 案 A A A A A A A A A A B B B B B B B B B B C C C C C C C C C C D D D D D D D D D D 1.( ) 十六进制数(C2) 十六进制用 8421 余 3 码表示为 11110100。 2.( )要构成容量为 4K×8 的 RAM,需要 16 片容量为 256×8 的 RAM。 3.( )F = ,则 F 的反函数 4.( )N 个逻辑变量共有 2N 个最小项

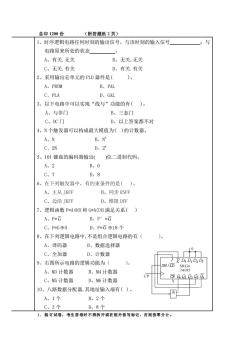

总印1200价 (附答题纸2页) 1、时序逻辑电路任何时刻的输出信号,与该时刻的输入信号_ 一;与 电路原来所处的状态 A、有关.无关 B、无关.无关 C、无关.有关 D、有关.有关 2、采用输出宏单元的PLD器件是( A、PROM B、PAL C、PLA D、GAL 3、以下电路中可以实现“线与”功能的有()。 A、与非门 B、三态门 C、0C门 D、以上答案都不对 4、N个触发器可以构成最大模值为()的计数器。 A、N B、N2 C、2N D、2 5、101键盘的编码器输出()位二进制代码。 A、2 B、6 C、7 D、8 6、在下列触发器中,有约束条件的是()。 A、主从JKFF B、同步RSFF C、边沿JKFF D、维阻DFF 7、逻辑函数F=A⊕B和G=A⊙B满足关系() A、F=G B、F'=G C、F=G⊕0 D、F=G⊕18个 8、在下列逻辑电路中,不是组合逻辑电路的有( A、译码器 B、数据选择器 10 C、全加器 D、计数器 9、右图所示电路的逻辑功能为( H/ID A、M3计数器 B、M4计数器 419 C、M5计数器 D、M6计数器 10、八路数据分配器,其地址输入端有()。 A、1个 B、2个 C、3个 D、8个 2,装订试卷,考生答卷时不得拆开或在框外留写标记,否则按零分计

总印 1200 份 (附答题纸 2 页) 1、时序逻辑电路任何时刻的输出信号,与该时刻的输入信号 ;与 电路原来所处的状态 。 A、有关.无关 B、无关.无关 C、无关.有关 D、有关.有关 2、采用输出宏单元的 PLD 器件是( )。 A、PROM B、PAL C、PLA D、GAL 3、以下电路中可以实现“线与”功能的有( )。 A、与非门 B、三态门 C、OC 门 D、以上答案都不对 4、N 个触发器可以构成最大模值为( )的计数器。 A、N B、N 2 C、2N D、2 N 5、101 键盘的编码器输出( )位二进制代码。 A、2 B、6 C、7 D、8 6、在下列触发器中,有约束条件的是( )。 A、主从 JKFF B、同步 RSFF C、边沿 JKFF D、维阻 DFF 7、逻辑函数 F=A⊕B 和 G=A⊙B 满足关系( ) A、F= G B、F′= G C、F=G⊕0 D、F= G ⊕18 个 8、在下列逻辑电路中,不是组合逻辑电路的有( )。 A、译码器 B、数据选择器 C、全加器 D、计数器 9、右图所示电路的逻辑功能为( )。 A、M3 计数器 B、M4 计数器 C、M5 计数器 D、M6 计数器 10、八路数据分配器,其地址输入端有( )。 A、1 个 B、2 个 C、3 个 D、8 个 2. 装 订 试卷 , 考生 答 卷时 不 得拆 开 或在 框 外留 写 标记 ,否 则 按零分计

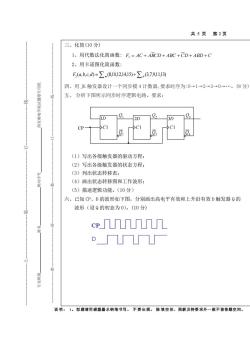

共5页第2页 三、化简(10分) I、用代数法化简函数:F=AC+ABCD+ABC+CD+ABD+C 2、用卡诺图化简函数 F5(a,bc,d0=∑.(8,10,121415+∑.37,91113) 四、用JK触发器设计一个同步模4计数器,要求时序为:0→1→2→3→0→.。(8分) 五、分析下图所示同步时序逻辑电路。要求: (1)写出各级触发器的驱动方程: (2)写出各级触发器的状态方程: (3)列出状态转移表: (4)画出状态转移图和工作波形 (5)描述逻辑功能。(10分) 六、已知CP、D的波形如下图,分别画出高电平有效和上升沿有效D触发器Q的 波形(设Q的初态为0)。(10分) cΠ几几几Π 说明:1。拟题请用碳塑墨水钢笔书写,不要出框。除填空体、图解及特要求外一般不留答题空间

共 5 页 第 2 页 说 明 : 1。 拟 题请用 碳塑墨 水钢 笔书写 。 不 要 出 框。 除 填 空 体、 图解 及特要 求外一 般不 留答题空 间。 - 上- 装- 订- 线- 专业班级 姓名 班内序号 西安邮电学院试题卷专用纸 - 密- 封- 装- 订- 线- 三、化简(10 分) 1、用代数法化简函数: F1 = AC + ABCD + ABC + CD + ABD + C 2、用卡诺图化简函数: ( , , , ) = (8,10,12,14,15) + (3,7,9,11,13) 2 m d F a b c d 四、用 JK 触发器设计一个同步模 4 计数器,要求时序为:0→1→2→3→0→.。(8 分) 五、 分析下图所示同步时序逻辑电路。要求: 1D Q1 Q2 C P Q1 Q2 2D 3D Q3 Q3 C1 C1 C1 (1)写出各级触发器的驱动方程; (2)写出各级触发器的状态方程; (3)列出状态转移表; (4)画出状态转移图和工作波形; (5)描述逻辑功能。(10 分) 六、已知 CP、D 的波形如下图,分别画出高电平有效和上升沿有效 D 触发器 Q 的 波形(设 Q 的初态为 0)。(10 分)

总印1200份 (附答题纸2页) 七、用PROM实现函数F=AC+B.C+A·B.C,画出阵列图。(10分) 八、有三套调节系统A、B和C,正常情况下必须有两套或两套以上的系统投入运 行,如出现其它情况则需发出中断信号F,设计发出中断信号的电路。要求: (1)用与非门实现。 (2)用一片四选一数据选择器实现 (3)用3线一8线译码器74138实现此电路。(12分) 九、用同步四位二进制计数器74161构成初始状态为0101的模11计数器。画 出状态转换图和连线图。74161的逻辑符号和功能表如下。(10分) 74161四位二进制时数器)功能表: 74161 输入端 输出端 CLRN LDN ENT ENP CLK D C B A QD QC QB QA X X XX XXX 0000 XX个d3d2d1d0d3d2d1d0 1 1 个 xXXXI 计数 0 XX XXX保持RC0=0 10 保持 2。装订试卷,考生答卷时不得拆开或在框外留写标记,否则按零分计

总印 1200 份 (附答题纸 2 页) 七、用 PROM 实现函数 F = AC + BC + A BC ,画出阵列图。(10 分) 八、有三套调节系统 A、B 和 C,正常情况下必须有两套或两套以上的系统投入运 行,如出现其它情况则需发出中断信号 F,设计发出中断信号的电路。要求: (1) 用与非门实现。 (2) 用一片四选一数据选择器实现。 (3) 用 3 线—8 线译码器 74138 实现此电路。(12 分) 九、用同步四位二进制计数器 74161 构成初始状态为 0101 的模 11 计数器。画 出状态转换图和连线图。74161 的逻辑符号和功能表如下。(10 分) 2. 装 订 试卷 , 考生 答 卷时 不 得拆 开 或在 框 外留 写 标记 ,否 则 按零分计

共5页第3页 3线一8线译码器74138真值表 STA STST A:AA万万万 X X X X X 1 11 X 1 0 0 X00 0 0 0 0 1 1 0 0 0 0 01111 0 74195功能表 入 输 出 CR SH/LD CP J K Do D1D2 D3 Qo Q1 Q2 Q3 Q 0 00001 ××d0d1d2d的 do dl d2 d3 d3 1 1 Q哈哈QQ贴Q贴 1 1 ↑00 0Q赔QQ贴Q呀 1 ↑10 QQ贴Q赠贴Q贴 1↑11XXXX 1Q8QQ贴Q贴 1 0×X×XX× Q片Q片Q3Q片Q片 4选1数据选择器真值表 A1 A Y 1 0 1 D 说明:1。拟题请用碳塑墨水钢笔书写,不要出框。除填空体、图解及特要求外一般不留答题空间

共 5 页 第 3 页 说 明 : 1。 拟 题请用 碳塑墨 水钢 笔书写 。 不 要 出 框。 除 填 空 体、 图解 及特要 求外一 般不 留答题空 间。 - 上- 装- 订- 线- 专业班级 姓名 班内序号 西安邮电学院试题卷专用纸 - 密- 封- 装- 订- 线- 11.分析下图的电路,设 Q1 端和 Q2 端的初态为零,Q1 端和 Q2 端的波形为: E. 以上答案都不对 12. 下图中 Q 端的状态方程为: A. Q D n = +1 B. n n n Q = Q J + K Q +1 C. n n Q = Q +1 D. n n Q = Q +1 E. 以上答案都不对 - 上- 装- 订- 线- 专业班级 姓名 班内序号 西安邮电学院试题卷专用纸 - 密- 封- 装- 订- 线- 3 线—8 线译码器 74138 真值表 STA STB STC A2 A1 A0 Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7 X 1 X X X X 1 1 1 1 1 1 1 1 X X 1 X X X 1 1 1 1 1 1 1 1 0 X X X X X 1 1 1 1 1 1 1 1 1 0 0 0 0 0 0 1 1 1 1 1 1 1 1 0 0 0 0 1 1 0 1 1 1 1 1 1 1 0 0 0 1 0 1 1 0 1 1 1 1 1 1 0 0 0 1 1 1 1 1 0 1 1 1 1 1 0 0 1 0 0 1 1 1 1 0 1 1 1 1 0 0 1 0 1 1 1 1 1 1 0 1 1 1 0 0 1 1 0 1 1 1 1 1 1 0 1 1 0 0 1 1 1 1 1 1 1 1 1 1 0 74195 功能表 4 选 1 数据选择器真值表

总印1200份 (附答题纸2页) 2。装订试卷,考生答卷时不得拆开或在框外留写标记,否则按零分计

总印 1200 份 (附答题纸 2 页) 2. 装 订 试卷 , 考生 答 卷时 不 得拆 开 或在 框 外留 写 标记 ,否 则 按零分计

按次数下载不扣除下载券;

注册用户24小时内重复下载只扣除一次;

顺序:VIP每日次数-->可用次数-->下载券;

- 西安邮电大学:《数字电路与逻辑设计》课程教学资源(试卷习题)2008数字电路与逻辑设计C卷(答案).doc

- 西安邮电大学:《数字电路与逻辑设计》课程教学资源(试卷习题)2008数字电路与逻辑设计B卷(答案).doc

- 西安邮电大学:《数字电路与逻辑设计》课程教学资源(试卷习题)2008数字电路与逻辑设计B卷(试题).doc

- 西安邮电大学:《数字电路与逻辑设计》课程教学资源(试卷习题)2008数字电路与逻辑设计A卷(答案).doc

- 西安邮电大学:《数字电路与逻辑设计》课程教学资源(试卷习题)2008数字电路与逻辑设计A卷(试题).doc

- 西安邮电大学:《数字电路与逻辑设计》课程教学资源(试卷习题)2007数字电路与逻辑设计B卷(试题).doc

- 西安邮电大学:《数字电路与逻辑设计》课程教学资源(试卷习题)2007数字电路与逻辑设计A卷(试题).doc

- 西安邮电大学:《数字电路与逻辑设计》课程教学资源(试卷习题)2007数字电路与逻辑设计B卷(答案).doc

- 西安邮电大学:《数字电路与逻辑设计》课程教学资源(试卷习题)2007数字电路与逻辑设计A卷(答案).doc

- 《数字电路与逻辑设计》课程各章习题(含解答)第九章 脉冲单元电路(2/2).doc

- 《数字电路与逻辑设计》课程各章习题(含解答)第九章 脉冲单元电路(1/2).doc

- 《数字电路与逻辑设计》课程各章习题(含解答)第八章 可编程逻辑器件及其应用.doc

- 《数字电路与逻辑设计》课程各章习题(含解答)第七章 半导体存储器.doc

- 《数字电路与逻辑设计》课程各章习题(含解答)第六章 时序逻辑电路.doc

- 《数字电路与逻辑设计》课程各章习题(含解答)第五章 集成触发器.doc

- 《数字电路与逻辑设计》课程各章习题(含解答)第四章 组合逻辑电路.doc

- 《数字电路与逻辑设计》课程各章习题(含解答)第三章 集成逻辑门.doc

- 《数字电路与逻辑设计》课程各章习题(含解答)第二章 逻辑函数及其简化.doc

- 《数字电路与逻辑设计》课程各章习题(含解答)第一章 绪论.doc

- 《数字电路与逻辑设计》课程实验指导(课程设计)设计四 数字电子密码锁.doc

- 西安邮电大学:《数字电路与逻辑设计》课程教学资源(试卷习题)2009数字电路与逻辑设计A卷(试题).doc

- 西安邮电大学:《数字电路与逻辑设计》课程教学资源(试卷习题)2009数字电路与逻辑设计A卷(答案).doc

- 西安邮电大学:《数字电路与逻辑设计》课程教学资源(试卷习题)2009数字电路与逻辑设计B卷(试题).doc

- 西安邮电大学:《数字电路与逻辑设计》课程教学资源(试卷习题)2009数字电路与逻辑设计B卷(答案).doc

- 西安邮电大学:《数字电路与逻辑设计》课程教学资源(试卷习题)2009数字电路与逻辑设计C卷(试题).doc

- 西安邮电大学:《数字电路与逻辑设计》课程教学资源(试卷习题)2009数字电路与逻辑设计C卷(答案).doc

- 西安邮电大学:《数字电路与逻辑设计》课程教学资源(试卷习题)2010数字电路与逻辑设计(48学时)A卷(试题).doc

- 西安邮电大学:《数字电路与逻辑设计》课程教学资源(试卷习题)2010数字电路与逻辑设计(48学时)A卷(答案).doc

- 西安邮电大学:《数字电路与逻辑设计》课程教学资源(试卷习题)2010数字电路与逻辑设计(48学时)B卷(试题).doc

- 西安邮电大学:《数字电路与逻辑设计》课程教学资源(试卷习题)2010数字电路与逻辑设计(48学时)B卷(答案).doc

- 西安邮电大学:《数字电路与逻辑设计》课程教学资源(试卷习题)2010数字电路与逻辑设计(48学时)C卷(试题).doc

- 西安邮电大学:《数字电路与逻辑设计》课程教学资源(试卷习题)2010数字电路与逻辑设计(48学时)C卷(答案).doc

- 西安邮电大学:《数字电路与逻辑设计》课程教学资源(试卷习题)2010数字电路与逻辑设计A卷(试题).doc

- 西安邮电大学:《数字电路与逻辑设计》课程教学资源(试卷习题)2010数字电路与逻辑设计A卷(答案).doc

- 西安邮电大学:《数字电路与逻辑设计》课程教学资源(试卷习题)2010数字电路与逻辑设计B卷(试题).doc

- 西安邮电大学:《数字电路与逻辑设计》课程教学资源(试卷习题)2010数字电路与逻辑设计B卷(答案).doc

- 西安邮电大学:《数字电路与逻辑设计》课程教学资源(试卷习题)2010数字电路与逻辑设计C卷(试题).doc

- 西安邮电大学:《数字电路与逻辑设计》课程教学资源(试卷习题)2010数字电路与逻辑设计C卷(答案).doc

- 《电路》课程教学资源(A)动态电路试题及解答.pdf

- 《电路》课程教学资源(A)课件(内容+例题,图片版)第12章 三相电路.ppt