《数字电路与逻辑设计》课程实验指导(课程设计)设计四 数字电子密码锁

4数字电子密码锁 设计目的与要求 目的:掌握矩阵式键盘的工作原理、设计方法:掌握译码器的应用:掌握状态机的 设计方法,掌握数码管的控制。 要求:设计一个数字电子密码锁,密码为3位,密码锁由键盘控制,显示采用数码 答及IDT 功能 1、密码输入:每按下一个数字键,要求在数码管上显示,并依次左移:输入错误 时,按退格键,清除前一个输入的数字:输入完毕,按确认键。 2、开锁:按开锁键,检查输入的密码是否正确,正确才开锁,成功。 3、上锁:按上锁键,可以直接上锁或者设定新密码上锁。 4、密码修改:按下修改键,必须先核对原密码,正确后可以输入3位数字,设为新 的密码。 5、报警:开锁输入密码,连续错误三次,则禁止输入密码,并发出报警信号,用 红灯一直亮表示。 6、解除报警:按复位键,解除报警状态,实际应用中复位键设置在其他部位,不 可设置在键盘上 7、 万能等 电锁维护者使用,在程序中暂时统一设置为999 8、其他要求:输入键盘为矩阵式,不使用直接式:条件允许时可以使用语音模块 代替指示灯的表示。 电路组成: 为达到以上功能,可将数字电子密码锁分为以下几个模块: 1、键盘接口电略: 键盘矩阵、键盘扫描、键盘消抖、键盘译码及按键存储。 2、密码锁控制电路: 数字按建输入、存储及清除 功能按键的设计:退格键、确认键、开锁键、上锁键、修改键、解除报警键: 密码清除、修改与存储。 密码锁的上锁与开锁。 3、输出显示电路 BCD译码、动态扫描电路、指示灯电路(或者为语音控制电路)。 三、功能电路的设计: 1、键盘接口电路:图1 (1)矩阵式键盘工作原理: 矩阵式键盘是一种常见的输入装置,在计算机、电话、手机、微波炉等各工电 子产品中被广泛应用。如图2所示为一4×4矩阵式键盘。 矩阵式键盘以行、列形式排列,图中为4行4列,键盘上的每一个按键盘其实 是个 关电路 当某键被按下时,该按键所 对应的位置就呈现逻辑0的状 ,键盘 的扫描可以以行扫或列扫方式进行,图中为行扫方式,KEYR3一KEYRO为扫描信 号,其中的某一位为0即扫描其中的一行,具体见表1

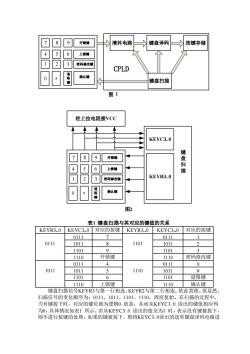

4 数字电子密码锁 一、 设计目的与要求: 目的:掌握矩阵式键盘的工作原理、设计方法;掌握译码器的应用;掌握状态机的 设计方法,掌握数码管的控制。 要求:设计一个数字电子密码锁,密码为3 位,密码锁由键盘控制,显示采用数码 管及LED灯。 功能: 1、 密码输入:每按下一个数字键,要求在数码管上显示,并依次左移;输入错误 时,按退格键,清除前一个输入的数字;输入完毕,按确认键。 2、 开锁:按开锁键,检查输入的密码是否正确,正确才开锁,成功。 3、 上锁:按上锁键,可以直接上锁或者设定新密码上锁。 4、 密码修改:按下修改键,必须先核对原密码,正确后可以输入3位数字,设为新 的密码。 5、 报警:开锁输入密码,连续错误三次,则禁止输入密码,并发出报警信号,用 红灯一直亮表示。 6、 解除报警:按复位键,解除报警状态,实际应用中复位键设置在其他部位,不 可设置在键盘上。 7、 万能密码:电锁维护者使用,在程序中暂时统一设置为999。 8、 其他要求:输入键盘为矩阵式,不使用直接式;条件允许时可以使用语音模块 代替指示灯的表示。 二、 电路组成: 为达到以上功能,可将数字电子密码锁分为以下几个模块: 1、键盘接口电路: 键盘矩阵、键盘扫描、键盘消抖、键盘译码及按键存储。 2、密码锁控制电路: 数字按键输入、存储及清除; 功能按键的设计:退格键、确认键、开锁键、上锁键、修改键、解除报警键; 密码清除、修改与存储。 密码锁的上锁与开锁。 3、输出显示电路 BCD译码、动态扫描电路、指示灯电路(或者为语音控制电路)。 三、功能电路的设计: 1、键盘接口电路:图1 (1)矩阵式键盘工作原理: 矩阵式键盘是一种常见的输入装置,在计算机、电话、手机、微波炉等各工电 子产品中被广泛应用。如图2所示为一4×4 矩阵式键盘。 矩阵式键盘以行、列形式排列,图中为4 行4 列,键盘上的每一个按键盘其实 是一个开关电路,当某键被按下时,该按键所对应的位置就呈现逻辑0的状态,键盘 的扫描可以以行扫或列扫方式进行,图中为行扫方式,KEYR3—KEYR0 为扫描信 号,其中的某一位为0即扫描其中的一行,具体见表1

789开做 清抖电路 键盘译码 按键存储 456上 123密码修政健 CPLD 键盘扫描 图1 经上拉电阻接VCC KEYC3.0 [刁89开模健 456上懒镜 盘扫描 123密码修 KEYR3.0 0 确认 图2 表1键盘扫描与其对应的键值的关系 KEYR3.0 KEYC3.0 对应的按键KEYR30KEYC3.0对应的按键 0111 011 0111 1011 8 1101 1011 2 1101 0 1101 开锁键 1110 密码修改键 0111 4 0111 0 1011 1011 5 1110 1011 1101 1101 退格键 1110 上锁键 确认键 键盘扫描信号KEYR3与第一行相连,KEYR2与第二行相连,依此类推,很显然, 扫描信号的变化顺序为:0111、1011、1101、1110,周而复始。在扫描的过程中, 当有键按下时,对应的键位就为逻辑0状态,从而从KEYC3.0读出的键值相应列 为0,具体情况如表1所示。若从KEYC3.0读出的值全为1时,表示没有键被按下 则不进行按键的处理。 如果的键被按下,则将KEYC3.0读出的送至键盘译码电路进

7 8 9 开锁键 4 5 6 上锁键 1 2 3 密码修改键 0 # 退 格 键 确认键 清抖电路 键盘译码 按键存储 键盘扫描 图 1 CPLD 7 8 9 开锁键 4 5 6 上锁键 1 2 3 密码修改键 0 # 退 格 键 确认键 经上拉电阻接VCC 图2 KEYC3.0 KEYR3.0 键 盘 扫 描 表1 键盘扫描与其对应的键值的关系 KEYR3.0 KEYC3.0 对应的按键 KEYR3.0 KEYC3.0 对应的按键 0111 0111 7 1101 0111 1 1011 8 1011 2 1101 9 1101 3 1110 开锁键 1110 密码修改键 1011 0111 4 1110 0111 0 1011 5 1011 # 1101 6 1101 退格键 1110 上锁键 1110 确认键 键盘扫描信号KEYR3与第一行相连,KEYR2与第二行相连,依此类推。很显然, 扫描信号的变化顺序为:0111、1011、1101、1110,周而复始。在扫描的过程中, 当有键按下时,对应的键位就为逻辑0 状态,从而从KEYC3.0 读出的键值相应列 为0,具体情况如表1 所示。若从KEYC3.0 读出的值全为1 时,表示没有键被按下, 则不进行按键的处理。如果的键被按下,则将KEYC3.0读出的送至键盘译码电路进

行译码。 (2)时钟产生电路 在一个系统的设计中,往往需要多种时钟信号,最方便的方法是利用一个自由 计数器来产生各种需要的频率 ,本电路需要:系统主时钟CLK 扫描状态产生时 ckouta和动态扫描时钟clkoutb,其中系统主时钟CLK为输入时钟, 由20MHZ晶振产 生。 程序清单: librarY ieee USEieee.std_logic_l164.ALL USE IEEE.STD_LOGIC_ARITH.ALL; USE IEEE STD LOGIC UNSIGNED ALL ENTITY clkdiv IS PORT(CLK·IN STD LOGIC clkouta,clkoutb:OUTSTD_LOGIC) END clkdiV: ARCHITECTURE rtl OF clkdiV IS SIGNAL CLKA:STD_LOGIC; Begin PROCESS (CLK) VARIABLE S:INTEGER RANGE 200 DOWNTO 0: Begin IF CLK'Event AND CLK=I'then IF S<200 THEN S=S+1, CLKA<-0 ELSES:-0, CLKA<=1 ENDIF; ENDIF END PROCESS PROCESS(CLKA) VARIABLE S:INTEGER RANGE 100 DOWNTO 0; Begin IF CLKA'Event andclka=l'ther IF S<10 THEN S=S+1 CLKOUTa<=0 clkoutb<='0': ELSIF S<20 THEN Q=g+1 CLKOUTa<=I' CLKOUTb<- ELSIF S<50 THEN S=S+1:

行译码。 (2)时钟产生电路 在一个系统的设计中,往往需要多种时钟信号,最方便的方法是利用一个自由 计数器来产生各种需要的频率。本电路需要:系统主时钟CLK、扫描状态产生时钟 clkouta和动态扫描时钟clkoutb,其中系统主时钟CLK为输入时钟,由20MHZ晶振产 生。 程序清单: LIBRARY ieee; USE ieee.std_logic_1164.ALL; USE IEEE.STD_LOGIC_ARITH.ALL ; USE IEEE.STD_LOGIC_UNSIGNED.ALL ; ENTITY clkdiv IS PORT (CLK: IN STD_LOGIC ; clkouta,clkoutb: OUT STD_LOGIC); END clkdiV ; ARCHITECTURE rtl OF clkdiV IS SIGNAL CLKA:STD_LOGIC; Begin PROCESS (CLK) VARIABLE S:INTEGER RANGE 200 DOWNTO 0; Begin IF CLK'Event AND CLK='1' then IF S<200 THEN S:= S+1; CLKA<='0'; ELSE S:=0; CLKA<='1'; END IF; END IF; END PROCESS; PROCESS (CLKA) VARIABLE S:INTEGER RANGE 100 DOWNTO 0; Begin IF CLKA'Event AND CLKA='1' then IF S<10 THEN S:= S+1; CLKOUTa<='0'; clkoutb<='0'; ELSIF S<20 THEN S:=S+1; CLKOUTa<='1'; CLKOUTb<='0'; ELSIF S<50 THEN S:=S+1;

CLKOUTa<='I CLKOUTb<=1; ELSIF S<70 THEN S=S+1 CLKOUTa<=1' CLKOUTb<-0: ELSIF S<100 THEN g=g+1. CLKOUTa CLKOUTb<-0; ELSE S:=0; EnDIF: ENDIF: END PROCESS 说明,K时钟经过两次分频,得到扫描状态产生时钟心 uta和动态扫描时钟elkout 均是1KHZ,但是扫描状态产生时钟clkouta的高电平部分完全包含动态扫描时钟 clkoutb的高电平部分,目的在于先使用时钟clkouta的上升沿产生扫描状态的变化, 再使用时钟clkoutb的上升沿产生键盘扫描信号。 仿真波形: 1.0rs 20m8 3.0ms 4.0ms 50m (3) 键盘扫描电路 目标:提供键盘扫描信号SCAN OUT,即表1中的KEYR3.0,变化顺序依次为0111、 1011、1101、1110.依次重复出现。 程序清单: LIBRARYieee USEieee.std_logic_1164.ALL USE IEEE STD LOGIC ARITHALL USE IEEE.STD LOGIC UNSIGNED.ALL ENTITY scan Is PORT(CLKA CLKB INSTD LOGIC SCAN_STATE:OUTSTD_LOGIC_VECTOR(1 DOWNTO0) SCAN OUT:OUT STD LOGIC VECTOR(3 downto0)): END scan; archiTecTUreitlof scan is SIGNAL S:STD LOGIC_VECTOR(I DOWNTO0). Begin PROCESS(CLKA)

CLKOUTa<='1'; CLKOUTb<='1'; ELSIF S<70 THEN S:=S+1; CLKOUTa<='1'; CLKOUTb<='0'; ELSIF S<100 THEN S:=S+1; CLKOUTa<='0'; CLKOUTb<='0'; ELSE S:=0; END IF; END IF; END PROCESS; end rtl; 说明:CLK时钟经过两次分频,得到扫描状态产生时钟clkouta和动态扫描时钟clkoutb 均是1KHZ,但是扫描状态产生时钟clkouta的高电平部分完全包含动态扫描时钟 clkoutb的高电平部分,目的在于先使用时钟clkouta的上升沿产生扫描状态的变化, 再使用时钟clkoutb的上升沿产生键盘扫描信号。 仿真波形: (3) 键盘扫描电路 目标:提供键盘扫描信号SCAN_OUT,即表1 中的KEYR3.0,变化顺序依次为0111、 1011、1101、1110. . . .依次重复出现。 程序清单: LIBRARY ieee; USE ieee.std_logic_1164.ALL; USE IEEE.STD_LOGIC_ARITH.ALL ; USE IEEE.STD_LOGIC_UNSIGNED.ALL ; ENTITY scan IS PORT (CLKA,CLKB: IN STD_LOGIC ; SCAN_STATE: OUT STD_LOGIC_VECTOR(1 DOWNTO 0); SCAN_OUT: OUT STD_LOGIC_VECTOR (3 downto 0)); END scan ; ARCHITECTURE rtl OF scan IS SIGNAL S:STD_LOGIC_VECTOR(1 DOWNTO 0); Begin PROCESS (CLKA)

Begin IF CLKA'Event AND CLKA=1'then 9=S+1: ENDIF; END PROCESS: PROCESS(CLKB,S) Reoin IF CLKB'Event AND CLKB=1'then CASES IS WHEN "00"=>SCAN_OUTSCAN_OUTSCAN OUTSCAN_OUTSCAN OUT<="1111" END CASE; SCAN_STATE<-S: ENDIF; END PROCESS END IL 说明:程序中,S信号是用来产生扫描信号的四个状态SCAN_STAT正:O0、O1、10 11 再利用动态扫描时钟的上升沿产生扫描信号:0111、1011、1101、1110 仿真波形: 40s 60ms 00 (4)键盘消抖电路 因为按键大多是机械式开关,在开关切换的瞬间会在接解点出现来回弹跳的现 $】 其现象可用图3 表示。由图口 见 虽然 次键,实际产生的按键信号封 只跳动一次,将会造成误码判,认为是按了两次键。如果调整取样时钟周期,可 以发现抖现象得到了改善。 CLK 按键信号 去抖输出 图3

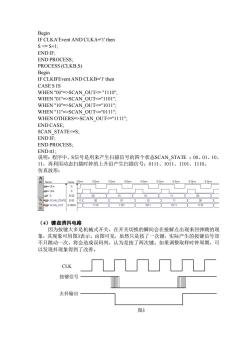

Begin IF CLKA'Event AND CLKA='1' then S SCAN_OUTSCAN_OUTSCAN_OUTSCAN_OUTSCAN_OUT<="1111"; END CASE; SCAN_STATE<=S; END IF; END PROCESS; END rtl ; 说明:程序中,S信号是用来产生扫描信号的四个状态SCAN_STATE :00、01、10、 11,再利用动态扫描时钟的上升沿产生扫描信号:0111、1011、1101、1110。 仿真波形: (4)键盘消抖电路 因为按键大多是机械式开关,在开关切换的瞬间会在接解点出现来回弹跳的现 象,其现象可用图3表示。由图可见,虽然只是按了一次键,实际产生的按键信号却 不只跳动一次,将会造成误码判,认为是按了两次键。如果调整取样时钟周期,可 以发现抖现象得到了改善。 CLK 按键信号 去抖输出 图3

通过时序图可见:在按键过程中可能有三种情况发生,①抖动发生在时钟的某 个上升沿,此时的输入信号为低电平,则输出为低电平:②抖动发生在时钟的某个 上升沿,但此时的输入信号抖动为高电平,由于按键(低电平)时间通常在200ms 以上,则在下一个上升沿出为低由平,③封动发生在时钟信的两个相邻上升 之间,则在第二个上升沿 出高由平 ,释放键盘时的情况类似 可风 期大于抖动时间而远小于按键时间,去抖电路即可正确识读按键次数。 一股健盘任 被按下和释放时会造成持续时间不大于10ms的信号抖动,而按键时间通常在200ms 以上,所以可以使用较低频率的时钟信号作为消抖时钟。 程序清单 LIBRARYieee: USE ieee.std_logic_1164.ALL USE IEEE.STD_LOGIC_ARITH.ALL: USE IEEE STD LOGIC UNSIGNED ALL ENTITY debouncing IS PORT (clkSCAN:IN STD_LOGIC; d in:IN STD LOGIC VECTORG DOWNTO0 d out:OUT STD LOGIC VECTOR(3 DOWNTO0)): END debouncing ARCHITECTURE a OF debou TEMPA,TEMPB,TEMPC,TEMPD,TEMPE:STD LOGIC VECTOR(3 DOWNTOO signal COUNT:STD LOGIC_VECTOR(DOWNTO0); BEGIN process(clkSCAN) begin if clkScAn'event and clkSCAn=0'then TEMPA="1000"THEN COUNT<= 1000" D_OUT<=D IN: FLse COUNT<=COUNT+I D0UT<="1111" END IF: ELS COUNT<-="0000" D OUT<="1111" END IE: END IF; end process process(clkSCAN)

通过时序图可见:在按键过程中可能有三种情况发生,①抖动发生在时钟的某 个上升沿,此时的输入信号为低电平,则输出为低电平;②抖动发生在时钟的某个 上升沿,但此时的输入信号抖动为高电平,由于按键(低电平)时间通常在200ms 以上,则在下一个上升沿输出为低电平;③抖动发生在时钟信号的两个相邻上升沿 之间,则在第二个上升沿输出高电平。释放键盘时的情况类似,可见,只要时钟周 期大于抖动时间而远小于按键时间,去抖电路即可正确识读按键次数。一般键盘在 被按下和释放时会造成持续时间不大于10ms的信号抖动,而按键时间通常在200ms 以上,所以可以使用较低频率的时钟信号作为消抖时钟。 程序清单: LIBRARY ieee; USE ieee.std_logic_1164.ALL; USE IEEE.STD_LOGIC_ARITH.ALL ; USE IEEE.STD_LOGIC_UNSIGNED.ALL ; ENTITY debouncing IS PORT (clkSCAN : IN STD_LOGIC; d_in:IN STD_LOGIC_VECTOR(3 DOWNTO 0); d_out: OUT STD_LOGIC_VECTOR(3 DOWNTO 0)); END debouncing ; ARCHITECTURE a OF debouncing IS signal TEMPA,TEMPB,TEMPC,TEMPD,TEMPE: STD_LOGIC_VECTOR(3 DOWNTO 0); signal COUNT: STD_LOGIC_VECTOR(3 DOWNTO 0); BEGIN process (clkSCAN) begin if clkSCAN'event and clkSCAN='0' then TEMPA="1000"THEN COUNT<="1000"; D_OUT<=D_IN; ELSE COUNT<=COUNT+1; D_OUT<="1111"; END IF; ELSE COUNT<="0000"; D_OUT<="1111"; END IF; END IF; end process ; process (clkSCAN)

begin if clkSCAN'event and clkSCAN='1'then TEMPBout numbout numb<"0001";-1

begin if clkSCAN'event and clkSCAN='1' then TEMPBout_numbout_numb<= "0001" ;-1

when "101011"=>out numbout numbout numbout_numbout numbout numbout numbout numbout numbout numbout numbout numb<="1111" end cas ENDIF: end process ENDa; 说明:键盘译码电路根据键盘输入数据dIN和扫描状态S进行译码out numb,数字 键为:0、1、2、3、4、5、6、7、8、9,功能键为:退格键、确认键、修改键、上 锁键和解锁键,out_numb=-“1111"表示无任何操作 仿真波形: kSCAN 1100人01 d IN y1110 out_numb 81111 1111 X1100光 1111 1100 (6)按键存储电路 键盘译码后,可以看出,译码值不等于“1111时表示有按键动作发生,当译码 值等于长时间“1111时,表示无按键动作发生,所以可以根据译码值产生按键动作 发生的标 信号和按键的译码值 程序清单: LIBRARY ieee: USEieee std logic 1164 AlL USE IEEE.STD LOGIC ARITH.ALL USE IEEE.STD_LOGIC UNSIGNED.ALL ENTITY num or fun DECIS PORT( cIkSCAN:IN STD LOGIC in_num:IN STD_LOGIC_VECTOR(3downto0): change_clk:out STD_LOGIC out_num:OUT STD_LOGIC_VECTOR(3downto 0)): END num or_fun DEC;

when "101011" =>out_numbout_numbout_numbout_numbout_numbout_numbout_numbout_numbout_numbout_numbout_numbout_numbout_numbout_numb<= "1111" ; end case ; END IF ; end process ; END a; 说明:键盘译码电路根据键盘输入数据d_IN和扫描状态S进行译码out_numb,数字 键为:0、1、2、3、4、5、6、7、8、9,功能键为:退格键、确认键、修改键、上 锁键和解锁键,out_numb=“1111”表示无任何操作。 仿真波形: (6)按键存储电路 键盘译码后,可以看出,译码值不等于“1111”时表示有按键动作发生,当译码 值等于长时间“1111”时,表示无按键动作发生,所以可以根据译码值产生按键动作 发生的标示信号和按键的译码值。 程序清单: LIBRARY ieee; USE ieee.std_logic_1164.ALL; USE IEEE.STD_LOGIC_ARITH.ALL ; USE IEEE.STD_LOGIC_UNSIGNED.ALL ; ENTITY num_or_fun_DEC IS PORT ( clkSCAN : IN STD_LOGIC ; in_num: IN STD_LOGIC_VECTOR (3 downto 0); change_clk: out STD_LOGIC; out_num : OUT STD_LOGIC_VECTOR(3 downto 0)); END num_or_fun_DEC ;

ARCHITECTUREaof num or fun dec is tmp_num:STD LOGIC VECTOR(3 downt PROCESS(clkSCAN) variable count,counta:std_logic_vector(2 downto0). hegin IF CLKSCANEVENTAND CLKSCAN='TTHEN if in_num="1111"then if count<7 then count:=count+1: else change clk<=0'; count:="111". counta:="000" end if: else temp_num<=in_num; counta:=counta+1; else counta ="011" change_clk<=1' f END IF· end process out num<=temp num; END a: 说明: 当按键译码值in num不等于“111时,按键发生标示信号change_clk-I,按 键译码输出值out_num等于按键译码值。 仿真波形: 00u2550s175200s25250us2530 TTTT out nu B111 110 2、电锁控制电路设计 电锁控制电路是整个电路的控制中心,主要完成如下功能: 1、数字按键输入部分

-****************************************************** ARCHITECTURE a OF num_or_fun_DEC IS signal temp_num:STD_LOGIC_VECTOR(3 downto 0); BEGIN PROCESS(clkSCAN) variable count,counta:std_logic_vector(2 downto 0); begin IF CLKSCAN'EVENT AND CLKSCAN = '1' THEN if in_num="1111"then if count<7 then count:=count+1; else change_clk<='0'; count:="111"; counta:="000"; end if; else temp_num<=in_num; count:="000"; if(counta<3)then counta:= counta+1; else counta:="011"; change_clk<='1'; end if; end if; END IF ; end process ; out_num<=temp_num; END a; 说明:当按键译码值in_num不等于“1111”时,按键发生标示信号change_clk='1',按 键译码输出值out_num等于按键译码值。 仿真波形: 2、电锁控制电路设计 电锁控制电路是整个电路的控制中心,主要完成如下功能: 1、 数字按键输入部分

如果输入数字键,第一个数字会从显示器的最右端开始显示,此后每新按一个 数字时,显示 器上的数字必须往左移动一位。 若想要更改输入的数字,可按退格键来清除前一个输入的数字,或按清除键清 除翰入的所有 数字,再重新输入3位数字。 既然设计的是三位电子密码锁,当输入的数字键绍过3位时,电路不应理会。 2、功能键输入部分 退格键:清除前一个输入的数字,如果数字全部清除,则回到前一个状态(例 如上锁或者解锁等 密码核对:在密码更改, 开锁之前必须先核对密码。 密码修改:按下此键先输入原密码,核对后将新输入的数字设定为新的密码。 上锁:按上锁键可以直接上锁。 解锁:检查输入的密码是否正确,正确才开锁。 万用密码:电锁维护者使用。 程序清单:三位电子密码锁 LIBRARYieee: USE ieee std logic 1164 AlL USE IEEE.STD LOGIC UN ED.ALL ENTITY control IS PORT(reset,d_clk:in std_logic; d in:In STD LOGIC VECTOR(3downto0) std o led flag.leda.ledb.lede:inout STD LOGIC VECTOR(3 downto0) END control; 零零***米零零米***米米**半率零米米*率*卡米家*半卡零家米米半米零零家米**米零家*米米率多零米率米 ARCHITECTURE a OF control IS TYPE STATE_TYPE IS (lock_idle,lock,unlock_idle,unlock,modify,new_num,alarm,num_one, num two.num three): SIGnAL state state type signal lock_rega,lock_regb,lock. rege:std_logic_vector(3 downto). signal lo ked,unlock_modify_flag:std_logic, BEGIN PROCESS(reset.state.d_in.d_clk) variable alarment:std_logic_vector(1 downto 0). BEGIN if reset=0'then

如果输入数字键,第一个数字会从显示器的最右端开始显示,此后每新按一个 数字时,显示 器上的数字必须往左移动一位。 若想要更改输入的数字,可按退格键来清除前一个输入的数字,或按清除键清 除输入的所有 数字,再重新输入3位数字。 既然设计的是三位电子密码锁,当输入的数字键超过3 位时,电路不应理会。 2、 功能键输入部分 退格键:清除前一个输入的数字,如果数字全部清除,则回到前一个状态(例 如上锁或者解锁等)。 密码核对:在密码更改,开锁之前必须先核对密码。 密码修改:按下此键先输入原密码,核对后将新输入的数字设定为新的密码。 上锁:按上锁键可以直接上锁。 解锁:检查输入的密码是否正确,正确才开锁。 万用密码:电锁维护者使用。 程序清单:三位电子密码锁 LIBRARY ieee; USE ieee.std_logic_1164.ALL; USE IEEE.STD_LOGIC_ARITH.ALL ; USE IEEE.STD_LOGIC_UNSIGNED.ALL ; ENTITY control IS PORT (reset,d_clk:in std_logic; d_in: IN STD_LOGIC_VECTOR (3 downto 0); led_alarm:out std_logic; led_flag,leda,ledb,ledc: inout STD_LOGIC_VECTOR (3 downto 0) ); END control ; -****************************************************** ARCHITECTURE a OF control IS TYPE STATE_TYPE IS (lock_idle,lock,unlock_idle,unlock,modify,new_num,alarm,num_one, num_two,num_three); SIGNAL state: STATE_TYPE; signal lock_rega,lock_regb,lock_regc:std_logic_vector(3 downto 0); signal locked,unlock_modify_flag:std_logic; BEGIN PROCESS (reset,state,d_in,d_clk) variable alarmcnt:std_logic_vector(1 downto 0); BEGIN if reset='0' then

按次数下载不扣除下载券;

注册用户24小时内重复下载只扣除一次;

顺序:VIP每日次数-->可用次数-->下载券;

- 《数字电路与逻辑设计》课程实验指导(课程设计)设计三 数字频率计的设计.doc

- 《数字电路与逻辑设计》课程实验指导(课程设计)设计二 数字抢答器的设计.doc

- 《数字电路与逻辑设计》课程实验指导(课程设计)设计一 自动交通控制系统.doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验四 组合电路设计(二).doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验十二 移位相加8位乘法器电路设计.doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验十一 电子琴电路设计.doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验十 LPM模块应用设计.doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验六 触发器设计.doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验八 计数器设计.doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验五 显示驱动电路设计.doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验九 序列检测器设计.doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验三 组合电路设计(一).doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验七 移位寄存器设计.doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验一 TTL门电路的逻辑变换及测试(3/3).doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验一 TTL门电路的逻辑变换及测试(2/3).doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验一 TTL门电路的逻辑变换及测试(1/3).doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验二 用文本输入法设计门电路.doc

- 西安邮电大学:《数字电路与逻辑设计》课程教学课件(PPT讲稿)第六章 时序逻辑电路(2/2).ppt

- 西安邮电大学:《数字电路与逻辑设计》课程教学课件(PPT讲稿)第八章 可编程逻辑器件及其应用.ppt

- 西安邮电大学:《数字电路与逻辑设计》课程教学课件(PPT讲稿)第九章 脉冲单元电路.ppt

- 《数字电路与逻辑设计》课程各章习题(含解答)第一章 绪论.doc

- 《数字电路与逻辑设计》课程各章习题(含解答)第二章 逻辑函数及其简化.doc

- 《数字电路与逻辑设计》课程各章习题(含解答)第三章 集成逻辑门.doc

- 《数字电路与逻辑设计》课程各章习题(含解答)第四章 组合逻辑电路.doc

- 《数字电路与逻辑设计》课程各章习题(含解答)第五章 集成触发器.doc

- 《数字电路与逻辑设计》课程各章习题(含解答)第六章 时序逻辑电路.doc

- 《数字电路与逻辑设计》课程各章习题(含解答)第七章 半导体存储器.doc

- 《数字电路与逻辑设计》课程各章习题(含解答)第八章 可编程逻辑器件及其应用.doc

- 《数字电路与逻辑设计》课程各章习题(含解答)第九章 脉冲单元电路(1/2).doc

- 《数字电路与逻辑设计》课程各章习题(含解答)第九章 脉冲单元电路(2/2).doc

- 西安邮电大学:《数字电路与逻辑设计》课程教学资源(试卷习题)2007数字电路与逻辑设计A卷(答案).doc

- 西安邮电大学:《数字电路与逻辑设计》课程教学资源(试卷习题)2007数字电路与逻辑设计B卷(答案).doc

- 西安邮电大学:《数字电路与逻辑设计》课程教学资源(试卷习题)2007数字电路与逻辑设计A卷(试题).doc

- 西安邮电大学:《数字电路与逻辑设计》课程教学资源(试卷习题)2007数字电路与逻辑设计B卷(试题).doc

- 西安邮电大学:《数字电路与逻辑设计》课程教学资源(试卷习题)2008数字电路与逻辑设计A卷(试题).doc

- 西安邮电大学:《数字电路与逻辑设计》课程教学资源(试卷习题)2008数字电路与逻辑设计A卷(答案).doc

- 西安邮电大学:《数字电路与逻辑设计》课程教学资源(试卷习题)2008数字电路与逻辑设计B卷(试题).doc

- 西安邮电大学:《数字电路与逻辑设计》课程教学资源(试卷习题)2008数字电路与逻辑设计B卷(答案).doc

- 西安邮电大学:《数字电路与逻辑设计》课程教学资源(试卷习题)2008数字电路与逻辑设计C卷(答案).doc

- 西安邮电大学:《数字电路与逻辑设计》课程教学资源(试卷习题)2008数字电路与逻辑设计C卷(试题).doc