《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验七 移位寄存器设计

实验七移位寄存器设计 1.实验目的 (a)掌握移位寄存器电路设计的方法。 (b)通过开发CPLD来实现时序逻辑电路的功能。 2.示例 1)设计一个四位串行输入并行输出的移位寄存器。该寄存器有一个串行数据输入 端d: 一个时钟输入端Ck: 一个四位数据输出端q。 源程序: Library ieee: Use ieee.std logic_1164.all; Entity shifter is Port(d,clk:instd_logic; q:out std_logic_vector(3 downto)); End; Architecture atl of shifter is Begin Process(clk) Begin if(elk'event ang clk=1)then q0<=d q1<=q0; q2<=ql; q3-q2 end if: end process, End; (2)74194移位寄存器的设计 源程序: Library ieee Use ieee.std_logic_1164.all: use ieee.std_logic_unsigned all Entity shiftl is Port(clk.Rd,sr.sl,sI.s0:in std logic. d:instd logie_vector(3 downto). oustd logie_vector(3 downto ) End: Architecture rtl of shiftl is Signal a:std_logic_vector(3 downto). Begin

实验七 移位寄存器设计 1.实验目的 (a)掌握移位寄存器电路设计的方法。 ( b) 通过开发 CPLD 来实现时序逻辑电路的功能。 2.示例 (1)设计一个四位串行输入并行输出的移位寄存器。该寄存器有一个串行数据输入 端 d;一个时钟输入端 clk;一个四位数据输出端 q。 源程序: Library ieee; Use ieee.std_logic_1164.all; Entity shifter is Port(d,clk:in std_logic; q:out std_logic_vector(3 downto 0)); End; Architecture atl of shifter is Begin Process(clk) Begin if( clk’event ang clk='1')then q0<=d; q1<=q0; q2<=q1; q3<=q2; end if; end process; End; (2)74194 移位寄存器的设计 源程序: Library ieee; Use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; Entity shift1 is Port(clk,Rd, sr,sl,s1,s0:in std_logic; d:in std_logic_vector(3 downto 0); q:out std_logic_vector(3 downto 0)); End; Architecture rtl of shift1 is Signal a: std_logic_vector(3 downto 0); Begin

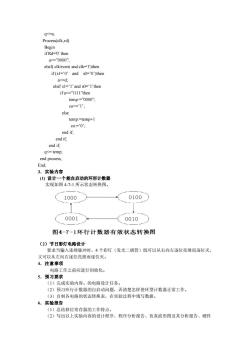

Begin if Rd=0'then a=70000” elsif clk'event and clk-'1')then if(sl='0'and s0='0")then elsif sl='1'and s0='I'then ifa<=”1111"then temp.="0000" else temp:=temp+l C0='0 end if; end if end if. q<=temp end process, End: 3.实验内容 ()设计 个能白启动的环形计新器 实现如图4-71所示状态转换图 (1000 0100 0001- (0010) 图4-7-1环行计数器有效状态转换图 (2)节日彩灯电路设计 要求当输入连续脉冲时,4个彩灯(发光二极管)既可以从右向左逐位亮继而逐位灭, 又可以从左向右逐位亮继而逐位灭 4.注意事项 电路工作之前应进行初始化。 5.预习要求 (1)完成实验内容。的申路设计任务 (2)预习环行计数器的自启动问恩,弄清楚怎样使环型计数器正常工作。 (3)自制各电路的状态转换表,在实验过程中填写数据。 6.实验报告 (1)总结移位寄存器的工作特点。 (2)写出以上实验内容的设计程序、程序分析报告、仿真波形图及其分析报告、硬件

q<=a; Process(clk,rd) Begin if Rd='0' then a<=”0000”; elsif( clk'event and clk='1')then if (s1=’0’ and s0=’0’)then a<=d; elsif s1=’1’ and s0=’1’then if a<=”1111”then temp:=”0000”; co<=’1’; else temp:=temp+1 co:=’0’; end if; end if; end if; q<= temp; end process; End; 3.实验内容 (1) 设计一个能自启动的环形计数器 实现如图 4-7-1 所示状态转换图。 (2)节日彩灯电路设计 要求当输入连续脉冲时,4 个彩灯(发光二极管)既可以从右向左逐位亮继而逐位灭, 又可以从左向右逐位亮继而逐位灭。 4.注意事项 电路工作之前应进行初始化。 5.预习要求 (1)完成实验内容。的电路设计任务。 (2)预习环行计数器的自启动问题,弄清楚怎样使环型计数器正常工作。 (3)自制各电路的状态转换表,在实验过程中填写数据。 6.实验报告 (1)总结移位寄存器的工作特点。 (2)写出以上实验内容的设计程序、程序分析报告、仿真波形图及其分析报告、硬件

测试和实验过程报告

测试和实验过程报告

按次数下载不扣除下载券;

注册用户24小时内重复下载只扣除一次;

顺序:VIP每日次数-->可用次数-->下载券;

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验一 TTL门电路的逻辑变换及测试(3/3).doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验一 TTL门电路的逻辑变换及测试(2/3).doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验一 TTL门电路的逻辑变换及测试(1/3).doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验二 用文本输入法设计门电路.doc

- 西安邮电大学:《数字电路与逻辑设计》课程教学课件(PPT讲稿)第六章 时序逻辑电路(2/2).ppt

- 西安邮电大学:《数字电路与逻辑设计》课程教学课件(PPT讲稿)第八章 可编程逻辑器件及其应用.ppt

- 西安邮电大学:《数字电路与逻辑设计》课程教学课件(PPT讲稿)第九章 脉冲单元电路.ppt

- 西安邮电大学:《数字电路与逻辑设计》课程教学课件(PPT讲稿)第七章 半导体存储器.ppt

- 《数字电路与逻辑设计》课程实验指导(数字电路实验)实验四 组合逻辑电路的设计(二).doc

- 《数字电路与逻辑设计》课程实验指导(数字电路实验)实验十 电子乒乓游戏机.doc

- 《数字电路与逻辑设计》课程实验指导(数字电路实验)实验六 小规模SSI计数器及其应用.doc

- 《数字电路与逻辑设计》课程实验指导(数字电路实验)实验八 移位寄存器及其应用.doc

- 《数字电路与逻辑设计》课程实验指导(数字电路实验)实验五 触发器及其应用.doc

- 《数字电路与逻辑设计》课程实验指导(数字电路实验)实验二 集成逻辑门的参数测试.doc

- 《数字电路与逻辑设计》课程实验指导(数字电路实验)实验九 数模(DA)和模数(AD)转换应用.doc

- 《数字电路与逻辑设计》课程实验指导(数字电路实验)实验三 组合逻辑电路的设计(一).doc

- 《数字电路与逻辑设计》课程实验指导(数字电路实验)实验七 计数器及其应用.doc

- 《数字电路与逻辑设计》课程实验指导(数字电路实验)实验一 TTL门电路的逻辑变换及测试.doc

- 西安邮电大学:《数字电路与逻辑设计》课程教学课件(PPT讲稿)第六章 时序逻辑电路(1/2).ppt

- 西安邮电大学:《数字电路与逻辑设计》课程教学课件(PPT讲稿)第五章 触发器.ppt

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验三 组合电路设计(一).doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验九 序列检测器设计.doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验五 显示驱动电路设计.doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验八 计数器设计.doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验六 触发器设计.doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验十 LPM模块应用设计.doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验十一 电子琴电路设计.doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验十二 移位相加8位乘法器电路设计.doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验四 组合电路设计(二).doc

- 《数字电路与逻辑设计》课程实验指导(课程设计)设计一 自动交通控制系统.doc

- 《数字电路与逻辑设计》课程实验指导(课程设计)设计二 数字抢答器的设计.doc

- 《数字电路与逻辑设计》课程实验指导(课程设计)设计三 数字频率计的设计.doc

- 《数字电路与逻辑设计》课程实验指导(课程设计)设计四 数字电子密码锁.doc

- 《数字电路与逻辑设计》课程各章习题(含解答)第一章 绪论.doc

- 《数字电路与逻辑设计》课程各章习题(含解答)第二章 逻辑函数及其简化.doc

- 《数字电路与逻辑设计》课程各章习题(含解答)第三章 集成逻辑门.doc

- 《数字电路与逻辑设计》课程各章习题(含解答)第四章 组合逻辑电路.doc

- 《数字电路与逻辑设计》课程各章习题(含解答)第五章 集成触发器.doc

- 《数字电路与逻辑设计》课程各章习题(含解答)第六章 时序逻辑电路.doc

- 《数字电路与逻辑设计》课程各章习题(含解答)第七章 半导体存储器.doc