西安邮电大学:《数字电路与逻辑设计》课程教学课件(PPT讲稿)第五章 触发器

西安邮电学院“校级优秀课程” 3 数字电路与逻辑设计 第五章触发器 西失郎電学院

1 数字电路与逻辑设计 第五章 触发器 西安邮电学院“校级优秀课程

第五章触发器 目的与要求: 1.理解触发器基本概念; 2.理解触发器的结构及工作原理; 3.掌握触发器逻辑功能的描述: 4.掌握触发器的典型应用。 重点与难点: 触发器外部逻辑功能、触发方式

2 目的与要求: 重点与难点: 第五章 触发器 1. 理解触发器基本概念; 2. 理解触发器的结构及工作原理; 3. 掌握触发器逻辑功能的描述; 4. 掌握触发器的典型应用。 触发器外部逻辑功能、触发方式

第五章触发器 5.1概述 5.2基本R-S触发器 5.3钟控(同步)触发器 5.4主从触发器 5.5边沿触发器 ⊙西长邹重孝院

3 5.1 概 述 5.2 基本R-S触发器 5.3 钟控(同步)触发器 5.4 主从触发器 5.5 边沿触发器 第五章 触发器

5.1概述 ·组合电路: 大类 结构上没有反馈线,功能上没有记忆功能; 辑电 电路的输出仅仅与当时的输入有关。 ·时序电路: 结构上有反馈线,功能上有记忆功能; 电路的输出不仅与当时的输入有关,而 且还与电路原来的状态有关

4 两 大 类 逻 辑 电 路 • 组合电路: • 时序电路: 结构上没有反馈线,功能上没有记忆功能; 电路的输出仅仅与当时的输入有关。 结构上有反馈线,功能上有记忆功能; 电路的输出不仅与当时的输入有关,而 且还与电路原来的状态有关。 5.1 概述

5.1概述 1.触发器: 时序逻辑电路的最基本单元;能够存储一位二进 制信息。 2.触发器特点: (1)有两个能够保持的稳定状态,分别用来表 示逻辑0和逻辑1。 (2)在适当输入信号作用下,可从一种状态翻 转到另一种状态;在输入信号取消后,能将 获得的新状态保存下来。 3触发器分类: 按触发方式分:电位触发方式、主从触发方式及边沿触发方式 按逻辑功能分:R-S触发器、D触发器、J-K触发器和T触发器

5 2.触发器特点: 3.触发器分类: 时序逻辑电路的最基本单元;能够存储一位二进 制信息。 (1)有两个能够保持的稳定状态,分别用来表 示逻辑0和逻辑1。 (2)在适当输入信号作用下,可从一种状态翻 转到另一种状态;在输入信号取消后,能将 获得的新状态保存下来。 按触发方式分:电位触发方式、主从触发方式及边沿触发方式 按逻辑功能分:R-S触发器、D触发器、J-K触发器和T触发器 1.触发器: 5.1 概述

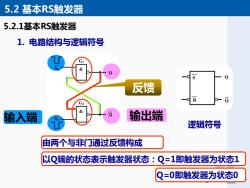

5.2基本RS触发器 5.2.1基本RS触发器 1.电路结构与逻辑符号 反馈 输入端 输出端 逻辑符号 由两个与非门通过反馈构成 以Q端的状态表示触发器状态:Q=1即触发器为状态1 Q=0即触发器为状态0

6 5.2.1基本RS触发器 SD & Q Q & RD G1 G2 S Q R Q 反馈 输入端 输出端 由两个与非门通过反馈构成 逻辑符号 1. 电路结构与逻辑符号 以Q端的状态表示触发器状态:Q=1即触发器为状态1 5.2 基本RS触发器 Q=0即触发器为状态0

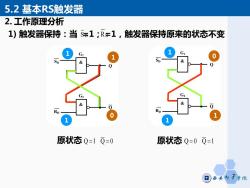

5.2基本RS触发器 2.工作原理分析 1)触发器保持:当Ss1;R于1,触发器保持原来的状态不变 原状态Q=1Q=0 原状态Q=0Q=1

7 2. 工作原理分析 SD & Q Q & RD G1 G2 1 1 SD & Q Q & RD G1 G2 1 0 0 1 1 1 原状态 Q =1 Q = 0 原状态 Q = 0 Q =1 1) 触发器保持:当 S =1 D ; R =1 D ,触发器保持原来的状态不变 5.2 基本RS触发器

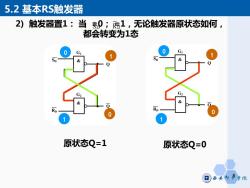

5.2基本RS触发器 2)触发器置1:当0;1,无论触发器原状态如何, 都会转变为1态 原状态Q=1 原状态Q=0

8 SD & Q Q & RD G1 G2 0 1 SD & Q Q & RD G1 G2 原状态Q=1 原状态Q=0 1 0 0 1 0 1 1 0 2) 触发器置1: 当 =0; =1,无论触发器原状态如何, 都会转变为1态 SD R D 5.2 基本RS触发器

5.2基本RS触发器 3)触发器置0:当元1;R0,无论触发器原状态如何, 都会转变为0态 原状态Q=X ⊙西卖郭是拳院

9 SD & Q Q & RD G1 G2 1 0 原状态Q=X x 1 0 3) 触发器置0: 当 =1; =0,无论触发器原状态如何, 都会转变为0态 SD R D 5.2 基本RS触发器

5.2基本RS触发器 4) 触发器禁止状态:当0;0时,触发器输出 Q和d均为1 而当$0R=0同时由0变成 1后,触发器新状态不能确 定 原状态Q=X 为避开禁止状态,输入信号不应同时出现 SL=0 RD=0 )西安1想学院

10 SD & Q Q & RD G1 G2 0 0 原状态Q=X 1 1 而当 =0; =0同时由0变成 1后,触发器新状态不能确 定 SD R D 为避开禁止状态,输入信号不应同时出现 SD =0; R D =0 4) 触发器禁止状态: 当 =0; =0时,触发器输出 Q和 均为1 SD R D Q 5.2 基本RS触发器

按次数下载不扣除下载券;

注册用户24小时内重复下载只扣除一次;

顺序:VIP每日次数-->可用次数-->下载券;

- 西安邮电大学:《数字电路与逻辑设计》课程教学课件(PPT讲稿)第四章 组合逻辑电路.ppt

- 西安邮电大学:《数字电路与逻辑设计》课程教学课件(PPT讲稿)第二章 逻辑函数及其简化.ppt

- 西安邮电大学:《数字电路与逻辑设计》课程教学课件(PPT讲稿)第三章 集成逻辑门.ppt

- 西安邮电大学:《数字电路与逻辑设计》课程教学课件(PPT讲稿)第一章 绪论.ppt

- 《数字电路与逻辑设计》课程教学大纲 Digital Circuit and Logic Design B.pdf

- 《数字电路与逻辑设计》课程教学大纲 Digital Circuit and Logic Design A.pdf

- 西安邮电大学:《现代通信网》课程教学课件(PPT讲稿)第十章 运输层.ppt

- 西安邮电大学:《现代通信网》课程教学课件(PPT讲稿)第十二章 宽带接入网.ppt

- 西安邮电大学:《现代通信网》课程教学课件(PPT讲稿)第十三章 宽带综合IP网.ppt

- 西安邮电大学:《现代通信网》课程教学课件(PPT讲稿)第八章 局域网.ppt

- 西安邮电大学:《现代通信网》课程教学课件(PPT讲稿)第九章 网络互连.ppt

- 西安邮电大学:《现代通信网》课程教学课件(PPT讲稿)第十一章 应用层.ppt

- 西安邮电大学:《现代通信网》课程教学课件(PPT讲稿)第六章 电话通信网.ppt

- 西安邮电大学:《现代通信网》课程教学课件(PPT讲稿)第三章 数据链路层.ppt

- 西安邮电大学:《现代通信网》课程教学课件(PPT讲稿)第七章 分组交换网.ppt

- 西安邮电大学:《现代通信网》课程教学课件(PPT讲稿)第一章 绪论.ppt

- 西安邮电大学:《现代通信网》课程教学课件(PPT讲稿)第五章 同步网.ppt

- 西安邮电大学:《现代通信网》课程教学课件(PPT讲稿)第四章 No.7信令网.ppt

- 西安邮电大学:《现代通信网》课程教学课件(PPT讲稿)第二章 传送网.ppt

- 西安邮电大学:《现代通信网》课程实验指导(讲稿)实验6 IAD108的数据配置.doc

- 西安邮电大学:《数字电路与逻辑设计》课程教学课件(PPT讲稿)第六章 时序逻辑电路(1/2).ppt

- 《数字电路与逻辑设计》课程实验指导(数字电路实验)实验一 TTL门电路的逻辑变换及测试.doc

- 《数字电路与逻辑设计》课程实验指导(数字电路实验)实验七 计数器及其应用.doc

- 《数字电路与逻辑设计》课程实验指导(数字电路实验)实验三 组合逻辑电路的设计(一).doc

- 《数字电路与逻辑设计》课程实验指导(数字电路实验)实验九 数模(DA)和模数(AD)转换应用.doc

- 《数字电路与逻辑设计》课程实验指导(数字电路实验)实验二 集成逻辑门的参数测试.doc

- 《数字电路与逻辑设计》课程实验指导(数字电路实验)实验五 触发器及其应用.doc

- 《数字电路与逻辑设计》课程实验指导(数字电路实验)实验八 移位寄存器及其应用.doc

- 《数字电路与逻辑设计》课程实验指导(数字电路实验)实验六 小规模SSI计数器及其应用.doc

- 《数字电路与逻辑设计》课程实验指导(数字电路实验)实验十 电子乒乓游戏机.doc

- 《数字电路与逻辑设计》课程实验指导(数字电路实验)实验四 组合逻辑电路的设计(二).doc

- 西安邮电大学:《数字电路与逻辑设计》课程教学课件(PPT讲稿)第七章 半导体存储器.ppt

- 西安邮电大学:《数字电路与逻辑设计》课程教学课件(PPT讲稿)第九章 脉冲单元电路.ppt

- 西安邮电大学:《数字电路与逻辑设计》课程教学课件(PPT讲稿)第八章 可编程逻辑器件及其应用.ppt

- 西安邮电大学:《数字电路与逻辑设计》课程教学课件(PPT讲稿)第六章 时序逻辑电路(2/2).ppt

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验二 用文本输入法设计门电路.doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验一 TTL门电路的逻辑变换及测试(1/3).doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验一 TTL门电路的逻辑变换及测试(2/3).doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验一 TTL门电路的逻辑变换及测试(3/3).doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验七 移位寄存器设计.doc