西安邮电大学:《数字电路与逻辑设计》课程教学课件(PPT讲稿)第六章 时序逻辑电路(1/2)

■■■■■ 西安邮电学院“校级优秀课程” 数字电路与逻辑设计 第六章时序逻辑电路 西奖那郎通学院

数字电路与逻辑设计 第六章 时序逻辑电路 西安邮电学院“校级优秀课程

第六章 时序罗辑电路 目的与要求: 1.掌握时序逻辑电路的定义、特点 2.掌握时序逻辑电路的分析方法 3.掌握时序逻辑电路的设计方法 重点与难点: 1.中、小规模时序逻辑电路的分析 2.中、小规模时序逻辑电路的设计

第六章 时序逻辑电路 目的与要求: 1.掌握时序逻辑电路的定义、特点 2.掌握时序逻辑电路的分析方法 3.掌握时序逻辑电路的设计方法 重点与难点: 1.中、小规模时序逻辑电路的分析 2.中、小规模时序逻辑电路的设计

第六章】 时序逻辑电路 6.1时序电路概述 6.2时序逻辑电路的分析 6.3寄存器、移位寄存器 6.4计数器 6.5采用中规模集成器件设计任意进制计数器 6.6采用小规模集成器件设计计数器

第六章 时序逻辑电路 6.1时序电路概述 6.2时序逻辑电路的分析 6.4计数器 6.5采用中规模集成器件设计任意进制计数器 6.3寄存器、移位寄存器 6.6采用小规模集成器件设计计数器

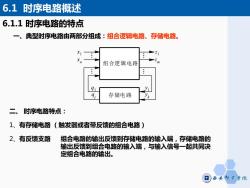

6.1时序电路概述 6.1.1时序电路的特点 一、典型时序电路由两部分组成:组合逻辑电路、存储电路。 X 组合逻辑电路 91 9 存储电路 二、时序电路特点: 1、有存储电路(触发器或者带反馈的组合电路) 2、有反馈支路 组合电路的输出反馈到存储电路的输入端,存储电路的 输出反馈到组合电路的输入端,与输入信号一起共同决 定组合电路的输出

6.1 时序电路概述 6.1.1 时序电路的特点 一、典型时序电路由两部分组成:组合逻辑电路、存储电路。 存储电路 组合逻辑电路 . . . x1 . x n z 1 z m q1 q j y1 y k 1、有存储电路 (触发器或者带反馈的组合电路) 2、有反馈支路 组合电路的输出反馈到存储电路的输入端,存储电路的 输出反馈到组合电路的输入端,与输入信号一起共同决 定组合电路的输出。 二、 时序电路特点:

6.1时序电路概述 6.1.2时序电路的分类 一、按照存储单元的状态改变是否在统一的时钟脉冲控制下同时发生分为: 同步时序电路和异步时序电路。 ●同步时序电路 存储电路的状态转换是在统一时钟控制下同步进行的 ●异步时序电路 设有统一时钟,存储电路状态变化不是同时发生的 二、按照输出信号的特点又分为: 米里(Meay)型时序电路和摩尔(Moore)型时序电路: ●米里型时序电路的输出函数为Z=F(X,Q),即某时刻的输出决定于该时刻 的外部输入和内部状态Q ●摩尔型时序电路的输出函数为Z=F(Q),即输出信号仅仅取决于存储电路 的状态,而和该时刻的外部输入信号无关

6.1.2 时序电路的分类 一、按照存储单元的状态改变是否在统一的时钟脉冲控制下同时发生分为: 同步时序电路和异步时序电路。 二、按照输出信号的特点又分为: 米里(Mealy)型时序电路和摩尔(Moore)型时序电路。 ●米里型时序电路的输出函数为 Z= F(X,Q),即某时刻的输出决定于该时刻 的外部输入X和内部状态Q ●摩尔型时序电路的输出函数为 Z = F(Q),即输出信号仅仅取决于存储电路 的状态,而和该时刻的外部输入信号无关 ●同步时序电路 ●异步时序电路 存储电路的状态转换是在统一时钟控制下同步进行的 没有统一时钟,存储电路状态变化不是同时发生的 6.1 时序电路概述

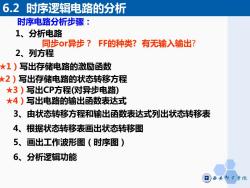

6.2时序逻辑电路的分析 时序电路分析步骤: 1、分析电路 同步o异步?FF的种类?有无输入输出? 2、列方程 ★1)写出存储电路的激励函数 ★2)写出存储电路的状态转移方程 ★3)写出CP方程(对异步电路) ★4)写出电路的输出函数表达式 3、由状态转移方程和输出函数表达式列出状态转移表 4、根据状态转移表画出状态转移图 5、画出工作波形图(时序图) 6、分析逻辑功能

时序电路分析步骤: ★1)写出存储电路的激励函数 ★2)写出存储电路的状态转移方程 ★4)写出电路的输出函数表达式 3、由状态转移方程和输出函数表达式列出状态转移表 4、根据状态转移表画出状态转移图 5、画出工作波形图(时序图) 6、分析逻辑功能 1、分析电路 同步or异步? FF的种类? 有无输入输出? 2、列方程 ★3)写出CP方程(对异步电路) 6.2 时序逻辑电路的分析

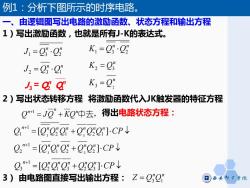

6.2时序逻辑电路的分析 例1:分析下图所示的时序电路。 :1J 解:题意分析 ☆本电路三级触发器有统一时钟CP,是同步时序电路, 时钟方程可以不写。 ☆ 三级JK触发器是在CP下降沿动作。 ☆1 电路输入信号CP,次态和输出只取决于存储器的初态, 属于摩尔型时序电路

解: ☆ 本电路三级触发器有统一时钟CP,是同步时序电路, 时钟方程可以不写。 ☆ 三级JK触发器是在CP下降沿动作。 题意分析 ☆ 电路输入信号CP,次态和输出只取决于存储器的初态, 属于摩尔型时序电路。 例1:分析下图所示的时序电路。 6.2 时序逻辑电路的分析 1J 1K 1 Q1 Q1 C1 & 1J 1K 2 Q2 Q2 C1 & 1J 1K 3 Q3 Q3 C1 & & & CP Z

6.2时序逻辑电路的分析 例1:分析下图所示的时序电路。 一、 由逻辑图写出电路的激励函数、状态方程和输出方程 1)写出激励函数,也就是所有J-K的表达式。 J1=Q302 K1=Q3·Q J2=Q3Q” K2=Q3 J=ga K;=O

例1:分析下图所示的时序电路。 6.2 时序逻辑电路的分析 1J 1K 1 Q1 Q1 C1 & 1J 1K 2 Q2 Q2 C1 & 1J 1K 3 Q3 Q3 C1 & & & CP Z n n J1 Q3 Q2 = n n K1 Q3 Q2 = n n J 2 Q3 Q1 = n K2 = Q3 n K Q2 3 = 一、由逻辑图写出电路的激励函数、状态方程和输出方程 1)写出激励函数,也就是所有J-K的表达式。 Q n n J 3 = 2 Q1

例1:分析下图所示的时序电路。 一、 由逻辑图写出电路的激励函数、状态方程和输出方程 1)写出激励函数,也就是所有J-K的表达式。 J=Q.0 K=.0 J2=Q0Q” K2=O J=g q K3=O" 2)写出状态转移方程将激励函数代入JK触发器的特征方程 Q+=JQ”+KQ”中去,得出电路状态方程: Qm-[gQg"+g9Q]CP↓ Q21=[g2"Q+Q"Q]CP↓ Q"=[g9"Q+Q52]CP↓ 3)由电路图直接写出输出方程:Z=QQ

将激励函数代入JK触发器的特征方程 n n J1 Q3 Q2 = = + + Q Q Q Q Q Q CP n n n n n n [ ] 1 2 2 1 2 3 3 = + + Q Q Q Q Q Q CP n n n n n n [ ] 2 1 3 2 3 1 3 3) 由电路图直接写出输出方程: n n Z = Q3 Q1 n n K1 Q3 Q2 = n n J 2 Q3 Q1 = n K2 = Q3 n K Q2 3 = 一、由逻辑图写出电路的激励函数、状态方程和输出方程 n 中去, n n Q = JQ + KQ +1 得出电路状态方程: = + + Q Q Q Q Q Q Q CP n n n n n n n [ ] 2 1 2 1 1 1 3 3 例1:分析下图所示的时序电路。 1)写出激励函数,也就是所有J-K的表达式。 2)写出状态转移方程 Q n n J 3 = 2 Q1

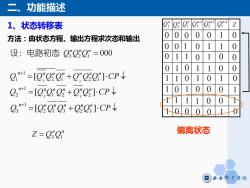

二、 功能描述 1、状态转移表 e;o"o" 方法:由状态方程、输出方程求次态和输出 0 0 0 0 0 0 001 0 1 0 设:电路初态QQ9”=000 011 011 0 0 01 0 1 1 0 0 Q,=[gQg+QQQ]CP↓ 1 1 0 1 0 1 0 Q2"-[g"2"2+Q,2]CP↓ 10 1 00 0 0 0 Q,+=[222"Q+Q2]CP↓ 100 0 0 Z=Q0” 偏离状态

二、功能描述 1、状态转移表 n Q3 n Q2 n Q1 1 3 n+ Q 1 2 n+ Q 1 1 n+ Q Z 3 2 1 = 000 n n n 设:电路初态 Q Q Q 0 0 0 0 0 1 0 0 0 1 1 0 0 1 1 1 0 0 0 1 0 1 0 1 1 0 1 1 0 1 0 1 0 0 1 1 1 1 1 1 0 0 0 方法:由状态方程、输出方程求次态和输出 0 1 0 1 0 0 0 1 0 0 0 0 1 = + + Q Q Q Q Q Q Q CP n n n n n n n [ ] 2 1 2 1 1 1 3 3 = + + Q Q Q Q Q Q CP n n n n n n [ ] 1 2 2 1 2 3 3 = + + Q Q Q Q Q Q CP n n n n n n [ ] 2 1 3 2 3 1 3 n n Z = Q3 Q1 偏离状态

按次数下载不扣除下载券;

注册用户24小时内重复下载只扣除一次;

顺序:VIP每日次数-->可用次数-->下载券;

- 西安邮电大学:《数字电路与逻辑设计》课程教学课件(PPT讲稿)第五章 触发器.ppt

- 西安邮电大学:《数字电路与逻辑设计》课程教学课件(PPT讲稿)第四章 组合逻辑电路.ppt

- 西安邮电大学:《数字电路与逻辑设计》课程教学课件(PPT讲稿)第二章 逻辑函数及其简化.ppt

- 西安邮电大学:《数字电路与逻辑设计》课程教学课件(PPT讲稿)第三章 集成逻辑门.ppt

- 西安邮电大学:《数字电路与逻辑设计》课程教学课件(PPT讲稿)第一章 绪论.ppt

- 《数字电路与逻辑设计》课程教学大纲 Digital Circuit and Logic Design B.pdf

- 《数字电路与逻辑设计》课程教学大纲 Digital Circuit and Logic Design A.pdf

- 西安邮电大学:《现代通信网》课程教学课件(PPT讲稿)第十章 运输层.ppt

- 西安邮电大学:《现代通信网》课程教学课件(PPT讲稿)第十二章 宽带接入网.ppt

- 西安邮电大学:《现代通信网》课程教学课件(PPT讲稿)第十三章 宽带综合IP网.ppt

- 西安邮电大学:《现代通信网》课程教学课件(PPT讲稿)第八章 局域网.ppt

- 西安邮电大学:《现代通信网》课程教学课件(PPT讲稿)第九章 网络互连.ppt

- 西安邮电大学:《现代通信网》课程教学课件(PPT讲稿)第十一章 应用层.ppt

- 西安邮电大学:《现代通信网》课程教学课件(PPT讲稿)第六章 电话通信网.ppt

- 西安邮电大学:《现代通信网》课程教学课件(PPT讲稿)第三章 数据链路层.ppt

- 西安邮电大学:《现代通信网》课程教学课件(PPT讲稿)第七章 分组交换网.ppt

- 西安邮电大学:《现代通信网》课程教学课件(PPT讲稿)第一章 绪论.ppt

- 西安邮电大学:《现代通信网》课程教学课件(PPT讲稿)第五章 同步网.ppt

- 西安邮电大学:《现代通信网》课程教学课件(PPT讲稿)第四章 No.7信令网.ppt

- 西安邮电大学:《现代通信网》课程教学课件(PPT讲稿)第二章 传送网.ppt

- 《数字电路与逻辑设计》课程实验指导(数字电路实验)实验一 TTL门电路的逻辑变换及测试.doc

- 《数字电路与逻辑设计》课程实验指导(数字电路实验)实验七 计数器及其应用.doc

- 《数字电路与逻辑设计》课程实验指导(数字电路实验)实验三 组合逻辑电路的设计(一).doc

- 《数字电路与逻辑设计》课程实验指导(数字电路实验)实验九 数模(DA)和模数(AD)转换应用.doc

- 《数字电路与逻辑设计》课程实验指导(数字电路实验)实验二 集成逻辑门的参数测试.doc

- 《数字电路与逻辑设计》课程实验指导(数字电路实验)实验五 触发器及其应用.doc

- 《数字电路与逻辑设计》课程实验指导(数字电路实验)实验八 移位寄存器及其应用.doc

- 《数字电路与逻辑设计》课程实验指导(数字电路实验)实验六 小规模SSI计数器及其应用.doc

- 《数字电路与逻辑设计》课程实验指导(数字电路实验)实验十 电子乒乓游戏机.doc

- 《数字电路与逻辑设计》课程实验指导(数字电路实验)实验四 组合逻辑电路的设计(二).doc

- 西安邮电大学:《数字电路与逻辑设计》课程教学课件(PPT讲稿)第七章 半导体存储器.ppt

- 西安邮电大学:《数字电路与逻辑设计》课程教学课件(PPT讲稿)第九章 脉冲单元电路.ppt

- 西安邮电大学:《数字电路与逻辑设计》课程教学课件(PPT讲稿)第八章 可编程逻辑器件及其应用.ppt

- 西安邮电大学:《数字电路与逻辑设计》课程教学课件(PPT讲稿)第六章 时序逻辑电路(2/2).ppt

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验二 用文本输入法设计门电路.doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验一 TTL门电路的逻辑变换及测试(1/3).doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验一 TTL门电路的逻辑变换及测试(2/3).doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验一 TTL门电路的逻辑变换及测试(3/3).doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验七 移位寄存器设计.doc

- 《数字电路与逻辑设计》课程实验指导(可编程逻辑实验)实验三 组合电路设计(一).doc