《计算机组成原理》课程教学课件(PPT讲稿)第4章 中央处理器

第4章中央处理器(教材第5章) 教学内容 ①CPU功能和组成②指令周期基本概念③硬布线 控制器设计技术④微程序控制器设计技术⑤流水处 理器,以及其他技术 教学重点与难点 ①分析CPU数据通路的,具体操作的微命令的确 定和实现过程的流程图描述②对指令具体字段、相 关寄存器的分析,微程序控制器、组合逻辑控制器 的分析、比较、设计③流水处理器的基本概念

第4章 中央处理器(教材第5章) 教学内容 ①CPU 功能和组成②指令周期基本概念③硬布线 控制器设计技术④微程序控制器设计技术⑤流水处 理器,以及其他技术 教学重点与难点 ①分析CPU 数据通路的,具体操作的微命令的确 定和实现过程的流程图描述②对指令具体字段、相 关寄存器的分析,微程序控制器、组合逻辑控制器 的分析、比较、设计③流水处理器的基本概念

第1节CPU的功能和组成 第2节指令周期 第3节时序信号和控制方式 第4节一个模型计算机和控制器初步设计 第5节硬布线控制器 第6节微程序控制器及微程序设计 第7节传统CPU介绍 第8节流水CPU 第9节RISC CPU

第1节 CPU 的功能和组成 第2节 指令周期 第3节 时序信号和控制方式 第4节 一个模型计算机和控制器初步设计 第5节 硬布线控制器 第6节微程序控制器及微程序设计 第7节 传统CPU介绍 第8节 流水CPU 第9节 RISC CPU

第1节CPU的功能和组成 一、CPU的功能 二、CPU的组成 三、CPU中的主要寄存器 四操作控制单元与时序产生器

第1节 CPU 的功能和组成 一、CPU的功能 二、CPU的组成 三、CPU中的主要寄存器 四操作控制单元与时序产生器

一、 CPU的功能 1指令控制 程序执行顺序控制 2操作控制 操作控制单元产生取出的一条指令的各种操作信号和 执行该指令的所须的各种操作信号. 3时间控制 对操作信号进行时间上的定时. 4数据加工 算术逻辑运算

一、CPU的功能 1 指令控制 程序执行顺序控制 2 操作控制 操作控制单元产生取出的一条指令的各种操作信号和 执行该指令的所须的各种操作信号. 3 时间控制 对操作信号进行时间上的定时. 4 数据加工 算术逻辑运算

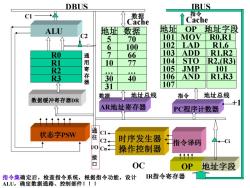

二、 CPU的组成 1运算器 ALU八寄存器1数据缓冲寄存器1状态条件寄存器PSW 主要功能在第2章中已讲 2当前CPU中新增加的部分 浮点运算器CACHE 3控制器 PC\指令寄存器R\指令译码器时序产生器操作控制器 主要功能:①从指令Cache中取指令,确定下一条指令在指令Cache 的位置 ②对指令译码引测试产生相应的操作控制信号 ③控制CPU与Cache \MEM\输入输出间的数据流动

二、CPU的组成 1 运算器 ALU \ 寄存器 \ 数据缓冲寄存器\状态条件寄存器PSW 主要功能在第2章中已讲 2 当前CPU中新增加的部分 浮点运算器\CACHE 3控制器 PC \ 指令寄存器IR \ 指令译码器\时序产生器\操作控制器 主要功能: 从指令Cache中取指令,确定下一条指令在指令Cache 的位置 对指令译码\测试产生相应的操作控制信号 控制CPU与Cache \MEM \ 输入\输出间的数据流动

DBUS IBUS 数据 指令 Cache Cache ALU 地细 数据 地 OP 地址字段 C2 5 7 101 MOV R0,R1 6 100 102 LAD R1,6 RO 66 103 ADD R1,R2 R1 用寄存器 10 77 104 STO R2,R3) R2 105 JMP 101 ●●● R3 30 40 106 AND R1,R3 31 107 数据 地址总线 指令 地址总线 数据缓冲寄存器DR AR地址寄存器 +1 PC程序计数器 状态字PSW 通C1 C2, 时序发生器 指令译码 操作控制器 口 OC OP 地址字段 指令集确定后,检查指令系统,根据指令功能,设计 R指令寄存器 ALU,确定数据通路、控制部件!!I

ALU C1 R0 R1 R2 R3 C2 通 用 寄 存 器 数据缓冲寄存器DR 状态字PSW 通 往 I/O 接 口 地址 数据 5 70 6 100 7 66 10 77 . . 30 40 31 数据 Cache AR地址寄存器 地址 OP 101 MOV 102 LAD 103 ADD 104 STO 105 JMP 106 AND 107 Cache 指令 地址字段 R0,R1 R1,6 R1,R2 R2,(R3) 101 R1,R3 PC程序计数器 +1 地址总线 地址总线 DBUS 数据 指令 时序发生器 操作控制器 指令译码 OP 地址字段 C1 C2 Cn Ci 指令集确定后,检查指令系统,根据指令功能,设计 IR指令寄存器 ALU,确定数据通路、控制部件!!! IBUS OC

三、CPU中的主要寄存器 CPU中至少有如下六类寄存器 1PC程序计数器 2指令寄存器 3地址寄存器 4数据缓冲器 5累加寄存器及通用寄存器 6状态条件寄存器PSW

三、CPU中的主要寄存器 CPU中至少有如下六类寄存器 1 PC程序计数器 2 指令寄存器 3 地址寄存器 4数据缓冲器 5累加寄存器及通用寄存器 6 状态条件寄存器PSW

程序计数器(PC) 指示(指出)下一条指令的内存地址

程序计数器(PC) 指示(指出)下一条指令的内存地址

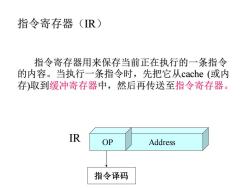

指令寄存器(R) 指令寄存器用来保存当前正在执行的一条指令 的内容。当执行一条指令时,先把它从cache(或内 存)取到缓冲寄存器中,然后再传送至指令寄存器。 IR OP Address 指令译码

指令寄存器(IR) 指令寄存器用来保存当前正在执行的一条指令 的内容。当执行一条指令时,先把它从cache (或内 存)取到缓冲寄存器中,然后再传送至指令寄存器。 OP Address IR 指令译码

数据地址寄存器(AR,MAR) 地址寄存器用来保存当前CPU所访问的Cache或 内存单元的地址,直到内存的读/写操作完成为止

数据地址寄存器(AR,MAR) 地址寄存器用来保存当前CPU所访问的 Cache或 内存单元的地址,直到内存的读/写操作完成为止

按次数下载不扣除下载券;

注册用户24小时内重复下载只扣除一次;

顺序:VIP每日次数-->可用次数-->下载券;

- 《计算机组成原理》课程教学课件(PPT讲稿)第7章 输入输出系统.ppt

- 《计算机组成原理》课程教学课件(PPT讲稿)第5章 存储系统.ppt

- 《计算机组成原理》课程教学课件(PPT讲稿)第8章 外围设备.ppt

- 《计算机组成原理》课程教学资源(实验指导)实验五 模型计算机与指令执行.doc

- 《计算机组成原理》课程教学资源(实验指导)实验四 数据通路.doc

- 《计算机组成原理》课程教学资源(实验指导)实验三 存储器.doc

- 《计算机组成原理》课程教学资源(实验指导)实验二 微程序控制器.doc

- 《计算机组成原理》课程教学资源(实验指导)TEC4模型计算机介绍.doc

- 《计算机组成原理》课程教学资源(实验指导)实验一 运算器.doc

- 《计算机组成原理》课程教学大纲 Computer Organization.doc

- 大连理工大学:《数据结构》课程教学课件(PPT讲稿)第八章 排序.ppt

- 大连理工大学:《数据结构》课程教学课件(PPT讲稿)第七章 查找.ppt

- 大连理工大学:《数据结构》课程教学课件(PPT讲稿)第六章 图.ppt

- 大连理工大学:《数据结构》课程教学课件(PPT讲稿)第五章 树.ppt

- 大连理工大学:《数据结构》课程教学课件(PPT讲稿)第四章 数组.ppt

- 大连理工大学:《数据结构》课程教学课件(PPT讲稿)第三章 栈和队列.ppt

- 大连理工大学:《数据结构》课程教学课件(PPT讲稿)第二章 线性表.ppt

- 大连理工大学:《数据结构》课程教学课件(PPT讲稿)第一章 绪言.ppt

- 厦门大学:《数据结构》课程教学大纲与教学规程 Data Structures.doc

- 《数据结构》课程教学资源(教材讲义)二叉树网上资料.doc

- 《计算机组成原理》课程教学课件(PPT讲稿)第2章 运算方法和运算器 第2节 定点加减运算及实现 第3节 定点乘法运算及实现 第4节 定点除法运算及实现 第5节 定点运算器的组成与结构 第6节 浮点运算方法和浮点运算器.ppt

- 《计算机组成原理》课程教学课件(PPT讲稿)第2章 运算方法和运算器 第1节 数据表示(数据与文字表示方法).ppt

- 《计算机组成原理》课程教学课件(PPT讲稿)第3章 指令系统.ppt

- 《计算机组成原理》课程教学课件(PPT讲稿)第6章 总线系统.ppt

- 《计算机组成原理》课程教学课件(PPT讲稿)第1章 计算机组成原理概述 Computer Organization.ppt

- 内蒙古科技大学:《C语言程序设计》课程教学大纲 C Language Programming.pdf

- 内蒙古科技大学:《C语言程序设计》课程授课教案(讲义)第七章 指针(四).doc

- 内蒙古科技大学:《C语言程序设计》课程授课教案(讲义)第九章 文件操作.doc

- 内蒙古科技大学:《C语言程序设计》课程授课教案(讲义)第七章 指针(三).doc

- 内蒙古科技大学:《C语言程序设计》课程授课教案(讲义)第八章 结构体与共用体.doc

- 内蒙古科技大学:《C语言程序设计》课程授课教案(讲义)第六章 数组 6.5 字符数组.doc

- 内蒙古科技大学:《C语言程序设计》课程授课教案(讲义)第七章 指针(二).doc

- 内蒙古科技大学:《C语言程序设计》课程授课教案(讲义)第六章 数组.doc

- 内蒙古科技大学:《C语言程序设计》课程授课教案(讲义)第七章 指针(一).doc

- 内蒙古科技大学:《C语言程序设计》课程授课教案(讲义)第五章 函数.doc

- 内蒙古科技大学:《C语言程序设计》课程授课教案(讲义)第六章 数组 6.2.doc

- 内蒙古科技大学:《C语言程序设计》课程授课教案(讲义)第六章 数组 6.3.doc

- 内蒙古科技大学:《C语言程序设计》课程授课教案(讲义)第六章 数组 6.3.doc

- 内蒙古科技大学:《C语言程序设计》课程授课教案(讲义)第四章 程序的控制结构(一).doc

- 内蒙古科技大学:《C语言程序设计》课程授课教案(讲义)第四章 程序的控制结构(二).doc