《计算机组成原理》课程教学资源(实验指导)实验四 数据通路

实验四数据通路组成实验 一、实验目的 (1)熟悉模型计算机的数据通路: (2)锻炼分析问题与解决问题的能力,在出现故障的情况下,独立分析故障现象 并排除故障。 二、实验电路 图8示出了数据通路实验电路图。该数据通路是将双端口RAM实验模块和一个双端口 通用寄存器堆F连接在一起形成的。通用寄存器堆连接运算器模块,本实验涉及其中的操 作数寄存器DR2。 由于双端口存储器RAM是三态输出,因而可以将它直接连接到数据总线DBUS上。此 外,DBUS上还连接着双端口通用寄存器堆。这样,写入存储器的数据可由通用寄存器堆提 供,而从存储器RAM读出的数据也可送到通用寄存器堆保存。 双端口存储器RAM己在前面己做过介绍,DR2在运算器的实验中使用过。通用寄存器 推RF(U32)由一个ISP1016实现,功能上与两个4位的MC14580并联构成的寄存器堆类 似。RF内含四个8位的通用寄存器R0、R1、R2、R3,带有一个写入端口和两个输出端口 从而可能同时写入一路数据,读出两路数据。写入端口取名为WR端口,连接一个8位的 暂存奇存器(U14)ER,这是一个74HC374.输出端口取名为RS端口(B端口)、RD端口 (A端口),连接运算器模块的两个操作数寄存器DR1、DR2。RS端口(B端口)的数据输 出还可通过一个8位的三态RS0(U15)直接向DBUS输出。 双端口的通用寄存器堆模块的控制信号中,RS1、RS0用于选择从RS端口(B端口) 读出的通用寄存器,RDL、RDO用于选择从RD端口(A端口)读出的通用寄存器。而WRI WRO则用于选择从WR端口写入的通用寄存器。WRD是写入控制信号,当WRD=I时,在 T2上升沿时刻,将暂存寄存器ER中的数据写入通用寄存器堆中由WR1、WR0选中的寄存 器:当WRD=O时,ER中的数据不写入通用寄存器中。LDER信号控制ER从DBUS写入 数据,当LDER=1时,在T4的上升沿,DBUS上的数据写入ER。RS.BUSA#信号则控制Rs 端口到DBUS的输出三态门,是一个低有效信号。以上控制信号各自连接一个二进制开关 K0-K15. 三、实验设备 (1)T正C-4计算机组成原理实验仪一台 (2)直流万用表一只 四、实验任务 (1)将实验电路与控制台的有关信号进行线路连接,方法同前面的实验 (2)用8位数据开关向RF中的四个通用寄存器分别置入以下数据:R0=0FH,R1=OF0H, R2=55H,R3=0AAH。 给RO置入OFH的步骤是:先用8位数码开关SW0SW7将OFH置入ER,并且选择 WR1=O、WRD=O、WRD=l,再将ER的数据置入RF。给其他通用寄存器置入数据的步聚

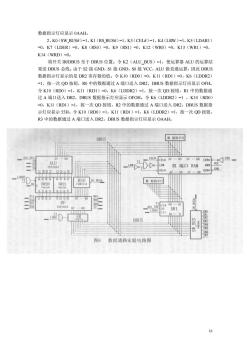

14 实验四 数据通路组成实验 一、实验目的 (1) 熟悉模型计算机的数据通路; (2) 锻炼分析问题与解决问题的能力,在出现故障的情况下,独立分析故障现象, 并排除故障。 二、实验电路 图 8 示出了数据通路实验电路图。该数据通路是将双端口 RAM 实验模块和一个双端口 通用寄存器堆 RF 连接在一起形成的。通用寄存器堆连接运算器模块,本实验涉及其中的操 作数寄存器 DR2。 由于双端口存储器 RAM 是三态输出,因而可以将它直接连接到数据总线 DBUS 上。此 外,DBUS 上还连接着双端口通用寄存器堆。这样,写入存储器的数据可由通用寄存器堆提 供,而从存储器 RAM 读出的数据也可送到通用寄存器堆保存。 双端口存储器 RAM 已在前面已做过介绍,DR2 在运算器的实验中使用过。通用寄存器 堆 RF(U32)由一个 ISP1016 实现,功能上与两个 4 位的 MC14580 并联构成的寄存器堆类 似。RF 内含四个 8 位的通用寄存器 R0、R1、R2、R3,带有一个写入端口和两个输出端口, 从而可能同时写入一路数据,读出两路数据。写入端口取名为 WR 端口,连接一个 8 位的 暂存寄存器(U14)ER,这是一个 74HC374。输出端口取名为 RS 端口(B 端口)、RD 端口 (A 端口),连接运算器模块的两个操作数寄存器 DR1、DR2。RS 端口(B 端口)的数据输 出还可通过一个 8 位的三态 RS0(U15)直接向 DBUS 输出。 双端口的通用寄存器堆模块的控制信号中,RS1、RS0 用于选择从 RS 端口(B 端口) 读出的通用寄存器,RD1、RD0 用于选择从 RD 端口(A 端口)读出的通用寄存器。而 WR1、 WR0 则用于选择从 WR 端口写入的通用寄存器。WRD 是写入控制信号,当 WRD=1 时,在 T2 上升沿时刻,将暂存寄存器 ER 中的数据写入通用寄存器堆中由 WR1、WR0 选中的寄存 器;当 WRD=0 时,ER 中的数据不写入通用寄存器中。LDER 信号控制 ER 从 DBUS 写入 数据,当 LDER=1 时,在 T4 的上升沿,DBUS 上的数据写入 ER。RS BUS#信号则控制 RS 端口到 DBUS 的输出三态门,是一个低有效信号。以上控制信号各自连接一个二进制开关 K0-K15。 三、实验设备 (1)TEC-4 计算机组成原理实验仪一台 (2) 直流万用表一只 四、实验任务 (1)将实验电路与控制台的有关信号进行线路连接,方法同前面的实验。 (2)用 8 位数据开关向 RF 中的四个通用寄存器分别置入以下数据:R0=0FH,R1=0F0H, R2=55H,R3=0AAH。 给 R0 置入 0FH 的步骤是:先用 8 位数码开关 SW0-SW7 将 0FH 置入 ER,并且选择 WR1=0、WRD=0、WRD=1,再将 ER 的数据置入 RF。给其他通用寄存器置入数据的步聚

与此类比。 (3)分别将R0至R3中的数据同时读入到DR2寄存器中和DBUS上,观察其数据是 否是存入R0至R3中的数据,并记录数据。其中DBUS上的数据可直接用指示灯显示,DR 中的数据可通过运算器ALU,用直通方式将其送往DBUS。 五、实验步骤与实验结果 (1)接线 JAR BUS#接VCC,禁止中断地址寄存器LAR向数据总线DBUS送数据。CER接GND 禁止存储器右端口工作。AR1NC接GND,禁止ARI加1。SI接GNDS2接GND,S0接 VC℃,使运算器ALU处于直通方式。M2接GND,使DR2选择寄存器堆F作为数据来源 置DP=1,DZ=0,DB=0,使实验系统开机后处于单拍状态。 KO接SW_BUS#,K1接RS_BUS#,K2接ALU_BUS,K3接CEI#,K4接LRW,K5 接LDARI,K6接LDDR2,K7接LDER,K8接RSO,K9接RSI,KI0接RDO,KII接RDI, KI2接WR0,K13接WR,K14接WRD 合上电源。按CR#按钮,使实验系绕处于初始状态 (2)向RF中的四个通用寄存器分别置入数据 KI (RS BUS#)=1,K2(ALU BUS)=0,K3(CEL#)=1,K4(LRW)=1,K5(LDARI) =0,K6(LDDR2)=0,K7(LDER)=0.K8(RS0)=0,K9(RSI)=0.K10(RD0)=0. K11(RD1)=0,K12(WR0)=0,K13(WR1)=0,K14(WRD)=0。 令K0(SW_BUS#)=0,K7(LDER)=1。置SW7-SW0为0FH,按一次QD按钮, 将OFH写入暂存寄存器ER。令K7(LDER)=O,K14(WRD)=l,K12(WRO)=O,K13 (WRI)=O,按一次QD按钮,将OFH(在ER中)写入RO寄存器。 令K0(SW BUS#)=0,K7(LDER)=1。置SW7-SW0为OFOH,按一次QD按钮, 将0FOH写入暂存寄存器ER。令K7(LDER)=0,K14(WRD)=1,K12(WRO)=1,K13 (WRI)=O,按一次QD按钮,将OFOH(在ER中)写入R1寄存器。 今K0(SW BUS#)=0,K7(LDER)=1。置SW7一SW0为55H,按一次OD按纽,将 55H写入暂存寄存器ER。令K7(LDER)=O,K14(WRD)=l, K12(WR0)-0,K13(WR1)=1,按一次QD按钮,将55H(在ER中)写入R2寄存器。 令K0(SW.BUS#)-0,K7(LDER)=1。置SW7-SW0为0AAH,按一次QD按钮, 将0AAH写入暂存寄存器ER。令K7(LDER)=0,K14(WRD)=1,K12(WR0)=1,K13 (WR1)=1,按一次OD按钮,将0AAH(在ER中)写入R3寄存器。 (3)分别将RO至R3中的数据同时读入到DR2寄存器中和DBUS上,观察其数据是 否是存入R0至R3中的数据。 (SW_BUS#)=1,K2 (ALU_BUS)=0,K3 (CEL#)=1,K4 (LRW)=1, K5(LDAR1)=0,K6(LDDR2)=0,K7(LDER)=0,K10(RD0)=0,KI1(RD1)=-0, K12(WR0)=0,K13(WR1)=0.K14(WRD)=0 将开关IR/DBUS至于DBUS位置。令KI(RS_BUSA#)=O,使寄存器堆中的数据送DBUS 总线。令K8(RS0)=O,K9(RSI)=O,R0中的数据通过B端口送DBUS,数据指示灯应 显示OFH。令K8(RS0)=l,K9(RSD=0,R1中的数据通过B端口送DBUS,数据指示 灯应显示0FOH。令K8(RS0)-O,K9(RSI)=1,R2中的数据通过B端口送DBUS,数 据指示灯应显示55H。令K8(RS0)=1,K9(RSI)=1,R3中的数据通过B端口送DBUS

15 与此类比。 (3)分别将 R0 至 R3 中的数据同时读入到 DR2 寄存器中和 DBUS 上,观察其数据是 否是存入 R0 至 R3 中的数据,并记录数据。其中 DBUS 上的数据可直接用指示灯显示,DR2 中的数据可通过运算器 ALU,用直通方式将其送往 DBUS。 五、实验步骤与实验结果 (1)接线 IAR BUS#接 VCC,禁止中断地址寄存器 IAR 向数据总线 DBUS 送数据。CER 接 GND, 禁止存储器右端口工作。AR1 INC 接 GND,禁止 ARI 加 1。S1 接 GND S2 接 GND,S0 接 VCC,使运算器 ALU 处于直通方式。M2 接 GND,使 DR2 选择寄存器堆 RF 作为数据来源。 置 DP=1,DZ=0,DB=0,使实验系统开机后处于单拍状态。 K0 接 SW BUS#,K1 接 RS BUS#,K2 接 ALU BUS,K3 接 CEL#,K4 接 LRW,K5 接 LDAR1,K6 接 LDDR2,K7 接 LDER,K8 接 RS0,K9 接 RSI,K10 接 RD0,K11 接 RD1, K12 接 WR0,K13 接 WR1,K14 接 WRD。 合上电源。按 CLR#按钮,使实验系统处于初始状态。 (2)向 RF 中的四个通用寄存器分别置入数据 令 K1(RS BUS#)=1,K2(ALU BUS)=0,K3(CEL#)=1,K4(LRW)=1,K5(LDAR1) =0,K6(LDDR2)=0,K7(LDER)=0,K8(RS0)=0,K9(RSI)=0,K10(RD0)=0, K11(RD1)=0,K12(WR0)=0,K13(WR1)=0,K14(WRD)=0。 令 K0(SW BUS#)=0,K7(LDER)=1。置 SW7—SW0 为 0FH,按一次 QD 按钮, 将 0FH 写入暂存寄存器 ER。令 K7(LDER)=0,K14(WRD)=1,K12(WR0)=0,K13 (WR1)=0,按一次 QD 按钮,将 0FH(在 ER 中)写入 R0 寄存器。 令 K0(SW BUS#)=0,K7(LDER)=1。置 SW7—SW0 为 0F0H,按一次 QD 按钮, 将 0F0H 写入暂存寄存器 ER。令 K7(LDER)=0,K14(WRD)=1,K12(WR0)=1,K13 (WR1)=0,按一次 QD 按钮,将 0F0H(在 ER 中)写入 R1 寄存器。 令 K0(SW BUS#)=0,K7(LDER)=1。置 SW7—SW0 为 55H,按一次 QD 按钮,将 55H 写入暂存寄存器 ER。令 K7(LDER)=0,K14(WRD)=1, K12(WR0)=0,K13(WR1)=1,按一次 QD 按钮,将 55H(在 ER 中)写入 R2 寄存器。 令 K0(SW BUS#)=0,K7(LDER)=1。置 SW7—SW0 为 0AAH,按一次 QD 按钮, 将 0AAH 写入暂存寄存器 ER。令 K7(LDER)=0,K14(WRD)=1,K12(WR0)=1,K13 (WR1)=1,按一次 QD 按钮,将 0AAH(在 ER 中)写入 R3 寄存器。 (3)分别将 R0 至 R3 中的数据同时读入到 DR2 寄存器中和 DBUS 上,观察其数据是 否是存入 R0 至 R3 中的数据。 1、令 K0(SW BUS#)=1,K2(ALU BUS)=0,K3(CEL#)=1,K4(LRW)=1, K5(LDAR1)=0,K6(LDDR2)=0,K7(LDER)=0,K10(RD0)=0,K11(RD1)=0, K12(WR0)=0,K13(WR1)=0,K14(WRD)=0。 将开关 IR/DBUS 至于 DBUS 位置。令 K1(RS BUS#)=0,使寄存器堆中的数据送 DBUS 总线。令 K8(RS0)=0,K9(RSI)=0,R0 中的数据通过 B 端口送 DBUS,数据指示灯应 显示 OFH。令 K8(RS0)=1,K9(RSI)=0,R1 中的数据通过 B 端口送 DBUS,数据指示 灯应显示 0FOH。令 K8(RS0)=0,K9(RSI)=1,R2 中的数据通过 B 端口送 DBUS,数 据指示灯应显示 55H。令 K8(RS0)=1,K9(RSI)=1,R3 中的数据通过 B 端口送 DBUS

数据指示灯应显示0AAH。 2.K0(SW.BUS#)=1.K1(RS.BUS#)=1.K3(CEL#)=1,K4(LRW)=1.K5(LDARI) =0,K7(LDER)=0,K8(RS0)=0,K9(RSI)-0,K12(WR0)=0,K13(WR1)=0, K14(WRD)=0. 将开关R/DBUS至于DBUS位置。令K2(ALU_BUS)=l,使运算器ALU的运算 果送DBUS总线。由于S2接GND,S1接GND,SO接VCC,ALU做直通运算,因此DBUS 数据指示灯品示的是DR2寄存器的值。今K10(RD0)=0.K11(RD1)=0.K6(LDDR2》 =l,按一次QD按钮,RO中的数据通过A端口送入DR2,DBUS数据指示灯应显示OFH。 令K10(RD0)=1,K11(RD1)=0.K6(LDDR2)=1,按一次OD按钮,R1中的数据通 过A端口送入DR2,DBUS数据指示灯应显示OFOH。令K6(LDDR2)=,KI0(RD0) =0,K11(RD1)=1,按一次QD按钮,R2中的数据通过A端口送入DR2,DBUS数据指 示打应显示55H。今K10(RD0)=1,K11(RD1)=1,K6(1DDR2)=1,按一次OD按钮. R3中的数据通过A端口送入DR2,DBUS数据指示灯应显示OAAH, 数指示 ALU 双端口RAM A7-AD OERW 数粼指示司 DBUS 图8数据通路实验电路图

16 数据指示灯应显示 0AAH。 2、K0(SW BUS#)=1,K1(RS BUS#)=1,K3(CEL#)=1,K4(LRW)=1,K5(LDAR1) =0,K7(LDER)=0,K8(RS0)=0,K9(RSI)=0,K12(WR0)=0,K13(WR1)=0, K14(WRD)=0。 将开关 IR/DBUS 至于 DBUS 位置。令 K2(ALU BUS)=1,使运算器 ALU 的运算结 果送 DBUS 总线。由于 S2 接 GND,S1 接 GND,S0 接 VCC,ALU 做直通运算,因此 DBUS 数据指示灯显示的是 DR2 寄存器的值。令 K10(RD0)=0,K11(RD1)=0,K6(LDDR2) =1,按一次 QD 按钮,R0 中的数据通过 A 端口送入 DR2,DBUS 数据指示灯应显示 OFH。 令 K10(RD0)=1,K11(RD1)=0,K6(LDDR2)=1,按一次 QD 按钮,R1 中的数据通 过 A 端口送入 DR2,DBUS 数据指示灯应显示 OFOH。令 K6(LDDR2)=1 ,K10(RD0) =0,K11(RD1)=1,按一次 QD 按钮,R2 中的数据通过 A 端口送入 DR2,DBUS 数据指 示灯应显示 55H。令 K10(RD0)=1,K11(RD1)=1,K6(LDDR2)=1,按一次 QD 按钮, R3 中的数据通过 A 端口送入 DR2,DBUS 数据指示灯应显示 OAAH

按次数下载不扣除下载券;

注册用户24小时内重复下载只扣除一次;

顺序:VIP每日次数-->可用次数-->下载券;

- 《计算机组成原理》课程教学资源(实验指导)实验三 存储器.doc

- 《计算机组成原理》课程教学资源(实验指导)实验二 微程序控制器.doc

- 《计算机组成原理》课程教学资源(实验指导)TEC4模型计算机介绍.doc

- 《计算机组成原理》课程教学资源(实验指导)实验一 运算器.doc

- 《计算机组成原理》课程教学大纲 Computer Organization.doc

- 大连理工大学:《数据结构》课程教学课件(PPT讲稿)第八章 排序.ppt

- 大连理工大学:《数据结构》课程教学课件(PPT讲稿)第七章 查找.ppt

- 大连理工大学:《数据结构》课程教学课件(PPT讲稿)第六章 图.ppt

- 大连理工大学:《数据结构》课程教学课件(PPT讲稿)第五章 树.ppt

- 大连理工大学:《数据结构》课程教学课件(PPT讲稿)第四章 数组.ppt

- 大连理工大学:《数据结构》课程教学课件(PPT讲稿)第三章 栈和队列.ppt

- 大连理工大学:《数据结构》课程教学课件(PPT讲稿)第二章 线性表.ppt

- 大连理工大学:《数据结构》课程教学课件(PPT讲稿)第一章 绪言.ppt

- 厦门大学:《数据结构》课程教学大纲与教学规程 Data Structures.doc

- 《数据结构》课程教学资源(教材讲义)二叉树网上资料.doc

- 厦门大学:《数据结构》课程教学课件(PPT讲稿)数据结构期末复习.ppt

- 厦门大学:《数据结构》课程教学课件(PPT讲稿)第四章 串(2/2).ppt

- 厦门大学:《数据结构》课程教学课件(PPT讲稿)第四章 串(1/2).ppt

- 厦门大学:《数据结构》课程教学课件(PPT讲稿)第十章 内部排序.ppt

- 厦门大学:《数据结构》课程教学课件(PPT讲稿)第十二章 文件.ppt

- 《计算机组成原理》课程教学资源(实验指导)实验五 模型计算机与指令执行.doc

- 《计算机组成原理》课程教学课件(PPT讲稿)第8章 外围设备.ppt

- 《计算机组成原理》课程教学课件(PPT讲稿)第5章 存储系统.ppt

- 《计算机组成原理》课程教学课件(PPT讲稿)第7章 输入输出系统.ppt

- 《计算机组成原理》课程教学课件(PPT讲稿)第4章 中央处理器.ppt

- 《计算机组成原理》课程教学课件(PPT讲稿)第2章 运算方法和运算器 第2节 定点加减运算及实现 第3节 定点乘法运算及实现 第4节 定点除法运算及实现 第5节 定点运算器的组成与结构 第6节 浮点运算方法和浮点运算器.ppt

- 《计算机组成原理》课程教学课件(PPT讲稿)第2章 运算方法和运算器 第1节 数据表示(数据与文字表示方法).ppt

- 《计算机组成原理》课程教学课件(PPT讲稿)第3章 指令系统.ppt

- 《计算机组成原理》课程教学课件(PPT讲稿)第6章 总线系统.ppt

- 《计算机组成原理》课程教学课件(PPT讲稿)第1章 计算机组成原理概述 Computer Organization.ppt

- 内蒙古科技大学:《C语言程序设计》课程教学大纲 C Language Programming.pdf

- 内蒙古科技大学:《C语言程序设计》课程授课教案(讲义)第七章 指针(四).doc

- 内蒙古科技大学:《C语言程序设计》课程授课教案(讲义)第九章 文件操作.doc

- 内蒙古科技大学:《C语言程序设计》课程授课教案(讲义)第七章 指针(三).doc

- 内蒙古科技大学:《C语言程序设计》课程授课教案(讲义)第八章 结构体与共用体.doc

- 内蒙古科技大学:《C语言程序设计》课程授课教案(讲义)第六章 数组 6.5 字符数组.doc

- 内蒙古科技大学:《C语言程序设计》课程授课教案(讲义)第七章 指针(二).doc

- 内蒙古科技大学:《C语言程序设计》课程授课教案(讲义)第六章 数组.doc

- 内蒙古科技大学:《C语言程序设计》课程授课教案(讲义)第七章 指针(一).doc

- 内蒙古科技大学:《C语言程序设计》课程授课教案(讲义)第五章 函数.doc