《通信原理实验》课程电子教案(PPT讲稿)FPGA通信系统设计——第二讲 System Generator for DSP

System Generator for DSP XILINX This material exempt per Department of Commerce license exception TSU 2007 Xilinx,Inc.All Rights Reserved

This material exempt per Department of Commerce license exception TSU © 2007 Xilinx, Inc. All Rights Reserved System Generator for DSP

提纲 .System Generator概述 .基础入门 ·采样周期及多速率设计 ·数据类型及类型转换 。 控制逻辑及HDL协同仿真 .硬件协同仿真 ·系统集成 Intro to System Generator -02-3 2006 Xilinx.Inc.All Rights Reserved XILINX

Intro to System Generator - 02 - 3 © 2006 Xilinx, Inc. All Rights Reserved 提纲 • System Generator概述 • 基础入门 • 采样周期及多速率设计 • 数据类型及类型转换 • 控制逻辑及HDL协同仿真 • 硬件协同仿真 • 系统集成

提纲 .System Generator概述 .基础入门 ·采样周期及多速率设计 数据类型及类型转换 .控制逻辑及DL协同仿真 硬件协同仿真 ·系统集成 Intro to System Generator -02-4 2006 Xilinx.Inc.All Rights Reserved XILINX

Intro to System Generator - 02 - 4 © 2006 Xilinx, Inc. All Rights Reserved 提纲 • System Generator概述 • 基础入门 • 采样周期及多速率设计 • 数据类型及类型转换 • 控制逻辑及HDL协同仿真 • 硬件协同仿真 • 系统集成

为什么用System Generator做FPGA 的DSP设计 Sysgen把FPGA的设计流程嵌入到了Matlab/Simulink中,把 Simulink的DSP算法设计和FPGA的实现集成在了一起 通过Sysgen在Simulink里做的算法设计就是FPGA设计,可以 直接生成HDL代码、网表或bit文件 还可以生成HDL testbench/test vector 可以把自己写的HDL代码放在Simulink中和其它Sysgen的设 计一起作算法仿真,即HDL协同仿真(HDL仿真器与Simulink协 同) 可以通过硬件协同仿真加速仿真验证 仿真链路可以用JTAG下载电缆或以太网 Intro to System Generator -02-5 2006 Xilinx.Inc.All Rights Reserved XILINX

Intro to System Generator - 02 - 5 © 2006 Xilinx, Inc. All Rights Reserved 为什么用System Generator 做 FPGA 的DSP设计 • Sysgen 把 FPGA 的设计流程嵌入到了 Matlab/Simulink 中,把 Simulink 的 DSP 算法设计和 FPGA 的实现集成在了一起 • 通过 Sysgen 在 Simulink 里做的算法设计就是 FPGA 设计,可以 直接生成 HDL代码、网表或 bit文件 – 还可以生成HDL testbench/test vector • 可以把自己写的 HDL 代码放在 Simulink 中和其它 Sysgen 的设 计一起作算法仿真,即 HDL协同仿真(HDL仿真器与 Simulink 协 同) • 可以通过硬件协同仿真加速仿真验证 – 仿真链路可以用JTAG下载电缆或以太网

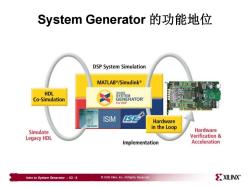

System Generator的功能地位 DSP System Simulation MATLAB/Simulink HDL XILINX SYSTEM Co-Simulation GENERATOR For DSP ISIM Hardware in the Loop Simulate Hardware Legacy HDL Verification Implementation Acceleration Intro to System Generator -02-6 2006 Xilinx,Inc.All Rights Reserved XILINX

Intro to System Generator - 02 - 6 © 2006 Xilinx, Inc. All Rights Reserved System Generator 的功能地位 ISIM

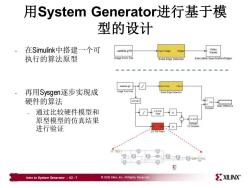

用System Generatorj进行基于模 型的设计 在Simulink中搭建一个可 satellite.gifR input image Edges Video Viewer 执行的算法原型 mage From File Sobel Edge Detection Executable Specification/Edges so量eg 再用Sysgen逐步实现成 mage From Fe Sobel Edge Detection 硬件的算法 Convert 通过比较硬件模型和 2DF月 原型模型的仿真结果 进行验证 2-D FIR FINe Intro to System Generator -02-7 2006 Xilinx,Inc.All Rights Reserved XILINX

Intro to System Generator - 02 - 7 © 2006 Xilinx, Inc. All Rights Reserved 用System Generator进行基于模 型的设计 • 在Simulink中搭建一个可 执行的算法原型 • 再用Sysgen逐步实现成 硬件的算法 – 通过比较硬件模型和 原型模型的仿真结果 进行验证

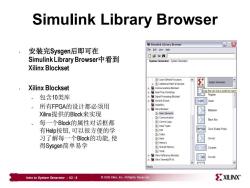

Simulink Library Browser Simulink Library Browser 回☒ 安装完Sysgen,后即可在 Eile Edit View Help ☐它女州「 Simulink Library Browser中看到 System Generator:System Generator Xilinx Blockset User-Defined Functions Additional Math Disorete System Generator Xilinx Blockset Communications Blockset ⊕Real-Time Workshop Drag this icon into a model to insert -包含10类库 Signal Processing Blockset Register Simulnk Extras 所有FPGA的设计都必须用 Statefiow 白inx Blockset EtBasher Xilinx提供的Block来实现 Basic Elements Communication Black Bax 每一个Block的属性对话框都 Control Logic Data Types 有Help按钮,可以很方便的学 DSP Clock Enable Probe Index 习了解每一个Block的功能,使 ☒h Concat 得Sysgeni简单易学 立☒Memory Shared Memory Constant 立Tools Xinx Reference Blockset Convert ④Xinx XtremeDSP Kit Ready Intro to System Generator -02-8 2006 Xilinx.Inc.All Rights Reserved XILINX

Intro to System Generator - 02 - 8 © 2006 Xilinx, Inc. All Rights Reserved Simulink Library Browser • 安装完Sysgen后即可在 Simulink Library Browser中看到 Xilinx Blockset • Xilinx Blockset – 包含10类库 – 所有FPGA的设计都必须用 Xilinx提供的Block来实现 – 每一个Block的属性对话框都 有Help按钮, 可以很方便的学 习了解每一个Block的功能, 使 得Sysgen简单易学

提纲 .System Generator概述 ·基础入门 ·采样周期及多速率设计 数据类型及类型转换 .控制逻辑及DL协同仿真 .硬件协同仿真 ·系统集成 Intro to System Generator -02-9 2006 Xilinx.Inc.All Rights Reserved XILINX

Intro to System Generator - 02 - 9 © 2006 Xilinx, Inc. All Rights Reserved 提纲 • System Generator概述 • 基础入门 • 采样周期及多速率设计 • 数据类型及类型转换 • 控制逻辑及HDL协同仿真 • 硬件协同仿真 • 系统集成

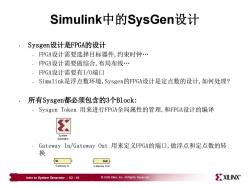

Simulink中的SysGen设计 ·Sysgen设计是FPGA的设计 FPGA设计需要选择目标器件,约束时钟. FPGA设计需要做综合,布局布线. .FPGA设计需要有I/O端口 Simulinkz是浮点数环境,Sysgent的FPGA设计是定点数的设计,如何处理? .所有Sysgen都必须包含的3个Block: -Sysgen Token用来进行FPGA全局属性的管理,和FPGA设计的编译 System Generator Gateway In/Gateway Out用来定义FPGA的端口,做浮点和定点数的转 换 Out Gateway In Gateway Out Intro to System Generator -02-10 2006 Xilinx.Inc.All Rights Reserved XILINX

Intro to System Generator - 02 - 10 © 2006 Xilinx, Inc. All Rights Reserved Simulink中的SysGen设计 • Sysgen设计是FPGA的设计 – FPGA设计需要选择目标器件,约束时钟. – FPGA设计需要做综合,布局布线. – FPGA设计需要有I/O端口 – Simulink是浮点数环境,Sysgen的FPGA设计是定点数的设计,如何处理? • 所有Sysgen都必须包含的3个Block: – Sysgen Token 用来进行FPGA全局属性的管理,和FPGA设计的编译 – Gateway In/Gateway Out 用来定义FPGA的端口,做浮点和定点数的转 换

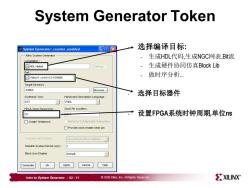

System Generator Token System Generator:counter_enabled 回☒ 选择编译目标: Xilinx System Generator 生成HDL代码,生成NGC网表,Bit流 Compllation: 包HDL Netlist Settings. 生成硬件协同仿真Block Lib Part: Virtex4 xc4v1x12-1011668 做时序分析 Target Directory /netlist Browse. 选择目标器件 Synthesis Tool: Hardware Description Language: XST VHDL FPGA Clock Period (ns): Clock Pin Location /1o 设置FPGA系统时钟周期,单位ns ☐Create Testbench import as Configurable Subsystem Provide clock enable clear pin Override with Doubles According to Block Settings Simulink System Period (sec): Block Icon Display: Default Generate OK Apply Cancel Help Intro to System Generator -02-11 2006 Xilinx.Inc.All Rights Reserved XILINX

Intro to System Generator - 02 - 11 © 2006 Xilinx, Inc. All Rights Reserved System Generator Token • 选择编译目标: – 生成HDL代码,生成NGC网表,Bit流 – 生成硬件协同仿真Block Lib – 做时序分析. • 选择目标器件 • 设置FPGA系统时钟周期,单位ns

按次数下载不扣除下载券;

注册用户24小时内重复下载只扣除一次;

顺序:VIP每日次数-->可用次数-->下载券;

- 《通信原理实验》课程电子教案(讲稿)FPGA通信系统设计——第二讲 实验二 Nexys 3实验板及设计软件.doc

- 《通信原理实验》课程电子教案(讲稿)FPGA通信系统设计——第三讲 实验三 DA芯片的型号及时序.pdf

- 《通信原理实验》课程电子教案(讲稿)FPGA通信系统设计——第三讲 实验三 DA芯片的型号及时序.doc

- 《通信原理实验》课程电子教案(PPT讲稿)FPGA通信系统设计——第一讲 XilinxFPGA介绍.ppt

- 《通信原理实验》课程电子教案(讲稿)FPGA通信系统设计——第一讲 实验一 FPGA.doc

- 《通信原理实验》课程电子教案(PPT讲稿)FPGA通信系统设计——第一讲 simulink教程(Simulink建模和仿真).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)CDMA移动通信系统实验.ppt

- 《通信原理实验》课程教学大纲 Experiments of the Communication Principle(非电类专业).doc

- 《通信原理实验》课程教学大纲 Experiments of the Communication Principle(电子信息工程专业).doc

- 《通信原理实验》课程教学大纲 Experiments of the Communication Principle(通信工程专业).doc

- 石河子大学:《电力电子技术》课程教学资源(课件讲稿)第9章 电力电子器件应用的共性问题(2016).pdf

- 石河子大学:《电力电子技术》课程教学资源(课件讲稿)第7章 PWM控制技术(2016).pdf

- 石河子大学:《电力电子技术》课程教学资源(课件讲稿)第5章 直流直流变流电路(2016).pdf

- 石河子大学:《电力电子技术》课程教学资源(课件讲稿)第3章 整流电路(2016).pdf

- 石河子大学:《电力电子技术》课程教学资源(课件讲稿)第4章 逆变电路(2016).pdf

- 石河子大学:《电力电子技术》课程教学资源(课件讲稿)第2章 电力电子器件(2016).pdf

- 石河子大学:《电力电子技术》课程教学课件(PPT讲稿)第1章 绪论(2016).ppt

- 石河子大学:《电力电子技术》课程教学课件(PPT讲稿)第3章 整流电路.ppt

- 石河子大学:《电力电子技术》课程教学课件(PPT讲稿)第2章 电力电子器件.ppt

- 石河子大学:《电力电子技术》课程教学课件(PPT讲稿)第1章 绪论(主讲:周伟绩).ppt

- 《通信原理实验》课程电子教案(讲稿)FPGA通信系统设计——第四讲 DDS信号发生器周期信号的傅里叶级数拟合.doc

- 《通信原理实验》课程电子教案(讲稿)FPGA通信系统设计——第四讲 实验四 DDS信号发生器与周期函数的傅里叶级数拟合.doc

- 《通信原理实验》课程电子教案(讲稿)FPGA通信系统设计——第四讲 方波信号展开为傅里叶级数.doc

- 《通信原理实验》课程电子教案(PPT讲稿)FPGA通信系统设计——第四讲 DDS信号发生器周期信号的傅里叶级数拟合.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)MATLAB与通信仿真电子教案_matlab在通信中的应用(PSK频带传输系统).doc

- 《通信原理实验》课程电子教案(PPT讲稿)MATLAB与通信仿真电子教案_matlab在通信中的应用(二进制基带系统).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)MATLAB与通信仿真电子教案_matlab在通信中的应用(模拟信号的数字传输).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)MATLAB与通信仿真电子教案_matlab在通信中的应用(模拟调制系统).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)MATLAB与通信仿真电子教案_第2章 matlab语言入门.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)MATLAB与通信仿真电子教案_第3章 图形处理与simulink仿真.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)MATLAB与通信仿真电子教案_第1章 matlab基础知识.ppt

- 《通信原理实验》课程电子教案(讲稿)MATLAB与通信仿真(英文)Chapter 1 Basic Matlab.doc

- 《通信原理实验》课程电子教案(PPT讲稿)MATLAB与通信仿真(英文)Chapter 2 Analog Modulation(AM,Amplitude Modulation).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)MATLAB与通信仿真(英文)Chapter 2 Analog Modulation(Conventional AM).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)MATLAB与通信仿真(英文)Chapter 2 Analog Modulation(SSB – AM).ppt

- 《通信原理实验》课程电子教案(讲稿)MATLAB与通信仿真(英文)Chapter 7 Spread Spectrum Communication Systems.doc

- 《通信原理实验》课程电子教案(PPT讲稿)MATLAB与通信仿真(英文)Chapter 2 Analog Modulation(Frequency Modulation、Phase Modulation).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)MATLAB与通信仿真(英文)Chapter 2 Transmitters and Receivers.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)MATLAB与通信仿真(英文)Chapter 3 Analog-to-Digital Conversion(Preview、Measure of Information、Quantization).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)MATLAB与通信仿真(英文)Chapter 3 Analog-to-Digital Conversion(Pulse Amplitude Modulation、Pulse Code Modulation).ppt