《通信原理实验》课程电子教案(讲稿)FPGA通信系统设计——第三讲 实验三 DA芯片的型号及时序

DA芯片的型号及时序 本综合实验系统的ADC DAC扩展卡上搭载了4路DA采样电 路。所选用的DA芯片是TI公司的8位微功耗轨到轨数模转换器 DAC081S101. DAC081S101是一种全功能、通用的8位电压输出的数模转换器, 它可以在+2.7V一+5.5V单端电源下工作,并且在3.6V电压下仅仅消 耗175uA电流。 DAC081S101的引脚图如下: VOUT 1 SYNC GND- 2 5 SCLK VA- -DIN 引脚描述 符号 引脚号 描述 VOUT DAC模拟输出电压 GND 2 对于所有电路的接地参考 VA 3 电源和参考输入。需解耦至GND

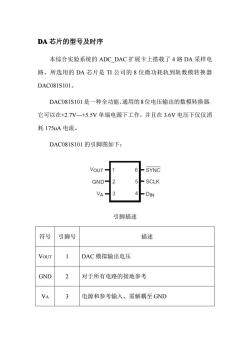

DA 芯片的型号及时序 本综合实验系统的 ADC_DAC 扩展卡上搭载了 4 路 DA 采样电 路。所选用的 DA 芯片是 TI 公司的 8 位微功耗轨到轨数模转换器 DAC081S101。 DAC081S101是一种全功能、通用的8位电压输出的数模转换器, 它可以在+2.7V—+5.5V 单端电源下工作,并且在 3.6V 电压下仅仅消 耗 175uA 电流。 DAC081S101 的引脚图如下: 引脚描述 符号 引脚号 描述 VOUT 1 DAC 模拟输出电压 GND 2 对于所有电路的接地参考 VA 3 电源和参考输入。需解耦至 GND

DIN 4 串行数据输入。在/SYNC信号下降以后,在SCLK 信号的下降沿,数据被输入16位移位寄存器。 SCL 5 串行时钟输入。在此信号的下降沿,数据被拍入输 K 入移位寄存器 /SYN 6 数据输入的帧同步输入。当此脚信号拉低,它使能 C 输入移位寄存器,数据在SCLK的下降沿被转移。 DAC在第16个时钟周期被更新,除非/SYNC信号 在第16个时钟前被拉高,在这种情况下/SYNC的 上升沿作为一个中断,写序列被DAC忽略。 工作额定值如下: 工作温度范围 -40°℃≤TA≤+105°℃ 电源电压,VA +2.7Vto5.5V 任意输入电压 -0.1Vto(Va+0.1V) 输出负载 0 to 1500 pF SCLK频率 Up to 30 MHz DAC081S101时序图:

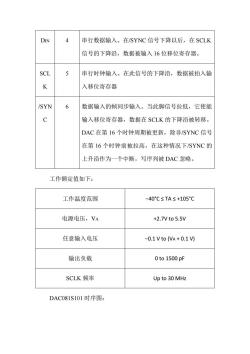

DIN 4 串行数据输入。在/SYNC 信号下降以后,在 SCLK 信号的下降沿,数据被输入 16 位移位寄存器。 SCL K 5 串行时钟输入。在此信号的下降沿,数据被拍入输 入移位寄存器 /SYN C 6 数据输入的帧同步输入。当此脚信号拉低,它使能 输入移位寄存器,数据在 SCLK 的下降沿被转移。 DAC 在第 16 个时钟周期被更新,除非/SYNC 信号 在第 16 个时钟前被拉高,在这种情况下/SYNC 的 上升沿作为一个中断,写序列被 DAC 忽略。 工作额定值如下: 工作温度范围 −40°C ≤ TA ≤ +105°C 电源电压,VA +2.7V to 5.5V 任意输入电压 −0.1 V to (VA + 0.1 V) 输出负载 0 to 1500 pF SCLK 频率 Up to 30 MHz DAC081S101 时序图:

DN 输入移位寄存器: 输入移位寄存器有16位。前2位是“无关”位,接下来的2位 决定了器件的工作模式,串行输入寄存器的内容在SCLK的第16个 下降沿转移到DAC寄存器。 输入寄存器的内容如下: MSB LSB XX PD1PDO D7 D6 D5 D4 2D1D0 DATA BITS 00 Normal Operation 0 1 1 ko to GND 1 0 100 k to GND Power-Down Modes 1 1 High Impedance 正常情况下,/SYNC信号保持低电平至少到SCLK信号的16个 下降沿,同时,DAC在SCLK信号的第16个下降沿进行更新。然而, 如果/SYNC信号在SCLK信号的第16个下降沿之前拉高,移位寄存 器被复位且写序列无效。DAC寄存器不会被更新,工作模式或者输 出电压没有改变。 在System Generator的设计中,为了满足信号输出时经过并串转

输入移位寄存器: 输入移位寄存器有 16 位。前 2 位是“无关”位,接下来的 2 位 决定了器件的工作模式,串行输入寄存器的内容在 SCLK 的第 16 个 下降沿转移到 DAC 寄存器。 输入寄存器的内容如下: 正常情况下,/SYNC 信号保持低电平至少到 SCLK 信号的 16 个 下降沿,同时,DAC 在 SCLK 信号的第 16 个下降沿进行更新。然而, 如果/SYNC 信号在 SCLK 信号的第 16 个下降沿之前拉高,移位寄存 器被复位且写序列无效。DAC 寄存器不会被更新,工作模式或者输 出电压没有改变。 在 System Generator 的设计中,为了满足信号输出时经过并串转

换后的时序要求,对DA部分的DN信号采取了组数操作,即在并串 转换前的8位数据高位添加4位0,低位添加20位0,同时/SYNC 信号保持低电平到SCLK信号的第32个下降沿。 欲了解该器件的详细信息,请查阅dac08lsl01.pdf文档。 DA时序设计 同AD的时序设计一致,DA芯片与FPGA之间进行通信的为 SCLK、/SYNC、DIN三个信号。 1)SCLK。DA转换芯片的串行时钟SCLK可高达3OMHz,我们 的设计中将SCLK设置为400KHz,因此,计数器的采样周 期为125。具体设置如下: ++ UFix 1 0 D2 UFix_1_0 D2 not Out clk CLK DAC Counter2 Inverte到

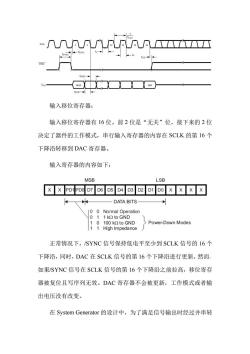

换后的时序要求,对 DA 部分的 DIN 信号采取了组数操作,即在并串 转换前的 8 位数据高位添加 4 位 0,低位添加 20 位 0,同时/SYNC 信号保持低电平到 SCLK 信号的第 32 个下降沿。 欲了解该器件的详细信息,请查阅 dac081s101.pdf 文档。 DA 时序设计 同 AD 的时序设计一致,DA 芯片与 FPGA 之间进行通信的为 SCLK、/SYNC、DIN 三个信号。 1) SCLK。DA 转换芯片的串行时钟 SCLK 可高达 30MHz,我们 的设计中将 SCLK 设置为 400KHz,因此,计数器的采样周 期为 125。具体设置如下:

Counter2 (Xilinx Counter) 口回X Hardware notes:Free running counters are the least expensive in hardware.A count limited counter is implemented by combining a counter with a comparator. Basic Advanced Implementation Counter type: ⊙Free running©Count limited Count to value Inf Count direction ⊙h○Down○Ip/Down Initial value 0 Step 2 Output Precision Output type Signed (2's comp)Unsigned Number of bits 1 Binary point 0 Optional Ports □Provide1 oad port Provide synchronous reset port □Provide enable port Explicit Sample Period Sample period source: Explicit Inferred from inputs Explicit period 125 K Cancel Help Apply 2)/SYNC。本设计中,为了使经过FPGA内部处理所得的结果通 过并串转换后能够满足时序的要求,两个SYNC高脉冲之间 相隔32个时钟(SCLK)周期。因此,/SYNC信号计数器的 采样周期为SCLK的2倍,即250。计数到31时产生高脉冲。 如下图所示:

2)/SYNC。本设计中,为了使经过 FPGA 内部处理所得的结果通 过并串转换后能够满足时序的要求,两个/SYNC 高脉冲之间 相隔 32 个时钟(SCLK)周期。因此,/SYNC 信号计数器的 采样周期为 SCLK 的 2 倍,即 250。计数到 31 时产生高脉冲。 如下图所示:

「+] UFix 5 0 D3 1 Bool D3 a=b Out Counter1 31 UFix 5 0.DT sync 6 DAC SYNC Constant4 Relational Counter1(Xilinx Counter) ▣回X Hardware notes:Free running counters are the least expensive in hardware.A count limited counter is implemented by combining a counter with a comparator. Basic Advanced Implementation Counter type: Free running Count limited Count to value 31 Count direction: ⊙Up○Down○Up/Down Initial value 0 Step 2 Output Precision Output type: ○Signed2 scomp) o Unsigned Number of bits 5 Binary point 0 Optional Ports ☐Provide1 oad port Provide synchronous reset port □Provide enable port Explicit Sample Period Sample period source: Explicit Inferred from inputs Explicit period 250 OK Cancel Help Apply 3)DN。根据DA转换的时序以及输入寄存器的内容格式,将经 过处理过后的8位并行数据进行组合:高4位补0+8位并行

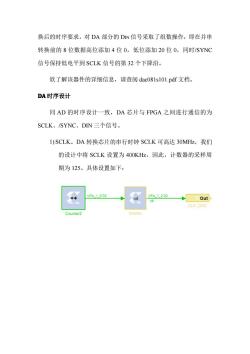

3) DIN。根据 DA 转换的时序以及输入寄存器的内容格式,将经 过处理过后的 8 位并行数据进行组合:高 4 位补 0 + 8 位并行

数据+低20位补0,随后进行并串转换。如下图: 0 UFix 4 0 D10 Constant1 UFix 32_0 D8 UFix_1 0 D3 Out dout seri UFx_20_0D10 DAC dataout Parallel to Serial Constant2 Concat Constant的属性可以通过双击看到,以Constant2为例,请看 下图: Constant2(Xilinx Constant Block) 回X Basic DSP48 Advanced Constant value可 Output Type ○Boolean⊙Fixed-point○Floating point Arithmetic type Unsigned Fixed-point Precision Number of bits 20 Binary point 0 Floating-point Precision ⊙Single○Double③Custom Exponent width 8 Fraction width 24 Sample Period ☑Sampled constant Sample period 40000 K Cancel Help Apply 实验要求: 产生周期为0.1s的方波、三角波或者锯齿波,在示波器上显示

数据 + 低 20 位补 0,随后进行并串转换。如下图: Constant 的属性可以通过双击看到,以 Constant2 为例,请看 下图: 实验要求: 产生周期为 0.1s 的方波、三角波或者锯齿波,在示波器上显示

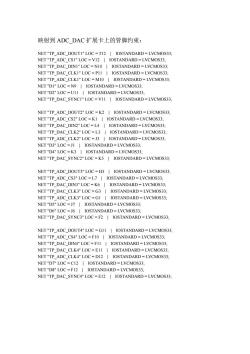

映射到ADC DAC扩展卡上的管脚约束: NET "TP ADC DOUTI"LOC =T12 IOSTANDARD=LVCMOS33; NET "TP ADC CS1"LOC V12 IOSTANDARD LVCMOS33; NET "TP DAC DINI"LOC N10 IOSTANDARD LVCMOS33; NET "TP DAC_CLK1"LOC=P11 IOSTANDARD=LVCMOS33; NET "TP_ADC_CLK1"LOC=M10 IOSTANDARD=LVCMOS33; NET "DI"LOC =N9 IOSTANDARD=LVCMOS33; NET "D2"LOC =U11 IOSTANDARD=LVCMOS33; NET"TP DAC SYNC1"LOC=V11 IOSTANDARD=LVCMOS33; NET "TP_ADC_DOUT2"LOC =K2 IOSTANDARD=LVCMOS33; NET "TP_ADC_CS2"LOC=K1 IOSTANDARD=LVCMOS33; NET "TP DAC DIN2"LOC=L4 IOSTANDARD=LVCMOS33; NET "TP DAC CLK2"LOC=L3 IOSTANDARD=LVCMOS33; NET "TP ADC CLK2"LOC=J3 IOSTANDARD=LVCMOS33; NET "D3"LOC =J1 IOSTANDARD=LVCMOS33: NET"D4"LOC =K3 IOSTANDARD=LVCMOS33: NET "TP DAC SYNC2"LOC=K5 IOSTANDARD=LVCMOS33: NET "TP ADC DOUT3"LOC =H3 IOSTANDARD=LVCMOS33; NET "TP_ADC_CS3"LOC=L7 IOSTANDARD=LVCMOS33: NET "TP_DAC_DIN3"LOC=K6 IOSTANDARD=LVCMOS33; NET "TP DAC CLK3"LOC =G3 IOSTANDARD=LVCMOS33: NET "TP ADC CLK3"LOC =GI IOSTANDARD=LVCMOS33; NET "D5"LOC =J7 IOSTANDARD=LVCMOS33: NET"D6"LOC=J6 IOSTANDARD=LVCMOS33; NET "TP DAC SYNC3"LOC=F2 IOSTANDARD=LVCMOS33; NET "TP_ADC_DOUT4"LOC =G11 IOSTANDARD=LVCMOS33; NET "TP_ADC_CS4"LOC=F10 IOSTANDARD=LVCMOS33; NET "TP DAC DIN4"LOC=F11 IOSTANDARD=LVCMOS33; NET"TP DAC CLK4"LOC=E11 IOSTANDARD=LVCMOS33: NET "TP_ADC_CLK4"LOC=D12 IOSTANDARD=LVCMOS33; NET "D7"LOC C12 IOSTANDARD =LVCMOS33 NET "D8"LOC F12 IOSTANDARD=LVCMOS33; NET "TP_DAC_SYNC4"LOC=E12 IOSTANDARD=LVCMOS33:

映射到 ADC_DAC 扩展卡上的管脚约束: NET "TP_ADC_DOUT1" LOC = T12 | IOSTANDARD = LVCMOS33; NET "TP_ADC_CS1" LOC = V12 | IOSTANDARD = LVCMOS33; NET "TP_DAC_DIN1" LOC = N10 | IOSTANDARD = LVCMOS33; NET "TP_DAC_CLK1" LOC = P11 | IOSTANDARD = LVCMOS33; NET "TP_ADC_CLK1" LOC = M10 | IOSTANDARD = LVCMOS33; NET "D1" LOC = N9 | IOSTANDARD = LVCMOS33; NET "D2" LOC = U11 | IOSTANDARD = LVCMOS33; NET "TP_DAC_SYNC1" LOC = V11 | IOSTANDARD = LVCMOS33; NET "TP_ADC_DOUT2" LOC = K2 | IOSTANDARD = LVCMOS33; NET "TP_ADC_CS2" LOC = K1 | IOSTANDARD = LVCMOS33; NET "TP_DAC_DIN2" LOC = L4 | IOSTANDARD = LVCMOS33; NET "TP_DAC_CLK2" LOC = L3 | IOSTANDARD = LVCMOS33; NET "TP_ADC_CLK2" LOC = J3 | IOSTANDARD = LVCMOS33; NET "D3" LOC = J1 | IOSTANDARD = LVCMOS33; NET "D4" LOC = K3 | IOSTANDARD = LVCMOS33; NET "TP_DAC_SYNC2" LOC = K5 | IOSTANDARD = LVCMOS33; NET "TP_ADC_DOUT3" LOC = H3 | IOSTANDARD = LVCMOS33; NET "TP_ADC_CS3" LOC = L7 | IOSTANDARD = LVCMOS33; NET "TP_DAC_DIN3" LOC = K6 | IOSTANDARD = LVCMOS33; NET "TP_DAC_CLK3" LOC = G3 | IOSTANDARD = LVCMOS33; NET "TP_ADC_CLK3" LOC = G1 | IOSTANDARD = LVCMOS33; NET "D5" LOC = J7 | IOSTANDARD = LVCMOS33; NET "D6" LOC = J6 | IOSTANDARD = LVCMOS33; NET "TP_DAC_SYNC3" LOC = F2 | IOSTANDARD = LVCMOS33; NET "TP_ADC_DOUT4" LOC = G11 | IOSTANDARD = LVCMOS33; NET "TP_ADC_CS4" LOC = F10 | IOSTANDARD = LVCMOS33; NET "TP_DAC_DIN4" LOC = F11 | IOSTANDARD = LVCMOS33; NET "TP_DAC_CLK4" LOC = E11 | IOSTANDARD = LVCMOS33; NET "TP_ADC_CLK4" LOC = D12 | IOSTANDARD = LVCMOS33; NET "D7" LOC = C12 | IOSTANDARD = LVCMOS33; NET "D8" LOC = F12 | IOSTANDARD = LVCMOS33; NET "TP_DAC_SYNC4" LOC = E12 | IOSTANDARD = LVCMOS33;

按次数下载不扣除下载券;

注册用户24小时内重复下载只扣除一次;

顺序:VIP每日次数-->可用次数-->下载券;

- 《通信原理实验》课程电子教案(讲稿)FPGA通信系统设计——第三讲 实验三 DA芯片的型号及时序.doc

- 《通信原理实验》课程电子教案(PPT讲稿)FPGA通信系统设计——第一讲 XilinxFPGA介绍.ppt

- 《通信原理实验》课程电子教案(讲稿)FPGA通信系统设计——第一讲 实验一 FPGA.doc

- 《通信原理实验》课程电子教案(PPT讲稿)FPGA通信系统设计——第一讲 simulink教程(Simulink建模和仿真).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)CDMA移动通信系统实验.ppt

- 《通信原理实验》课程教学大纲 Experiments of the Communication Principle(非电类专业).doc

- 《通信原理实验》课程教学大纲 Experiments of the Communication Principle(电子信息工程专业).doc

- 《通信原理实验》课程教学大纲 Experiments of the Communication Principle(通信工程专业).doc

- 石河子大学:《电力电子技术》课程教学资源(课件讲稿)第9章 电力电子器件应用的共性问题(2016).pdf

- 石河子大学:《电力电子技术》课程教学资源(课件讲稿)第7章 PWM控制技术(2016).pdf

- 石河子大学:《电力电子技术》课程教学资源(课件讲稿)第5章 直流直流变流电路(2016).pdf

- 石河子大学:《电力电子技术》课程教学资源(课件讲稿)第3章 整流电路(2016).pdf

- 石河子大学:《电力电子技术》课程教学资源(课件讲稿)第4章 逆变电路(2016).pdf

- 石河子大学:《电力电子技术》课程教学资源(课件讲稿)第2章 电力电子器件(2016).pdf

- 石河子大学:《电力电子技术》课程教学课件(PPT讲稿)第1章 绪论(2016).ppt

- 石河子大学:《电力电子技术》课程教学课件(PPT讲稿)第3章 整流电路.ppt

- 石河子大学:《电力电子技术》课程教学课件(PPT讲稿)第2章 电力电子器件.ppt

- 石河子大学:《电力电子技术》课程教学课件(PPT讲稿)第1章 绪论(主讲:周伟绩).ppt

- 石河子大学:《电力电子技术》课程教学课件(PPT讲稿)第4章 逆变电路.ppt

- 石河子大学:《电力电子技术》课程教学课件(PPT讲稿)第6章 交流交流变流电路.ppt

- 《通信原理实验》课程电子教案(讲稿)FPGA通信系统设计——第二讲 实验二 Nexys 3实验板及设计软件.doc

- 《通信原理实验》课程电子教案(PPT讲稿)FPGA通信系统设计——第二讲 System Generator for DSP.ppt

- 《通信原理实验》课程电子教案(讲稿)FPGA通信系统设计——第四讲 DDS信号发生器周期信号的傅里叶级数拟合.doc

- 《通信原理实验》课程电子教案(讲稿)FPGA通信系统设计——第四讲 实验四 DDS信号发生器与周期函数的傅里叶级数拟合.doc

- 《通信原理实验》课程电子教案(讲稿)FPGA通信系统设计——第四讲 方波信号展开为傅里叶级数.doc

- 《通信原理实验》课程电子教案(PPT讲稿)FPGA通信系统设计——第四讲 DDS信号发生器周期信号的傅里叶级数拟合.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)MATLAB与通信仿真电子教案_matlab在通信中的应用(PSK频带传输系统).doc

- 《通信原理实验》课程电子教案(PPT讲稿)MATLAB与通信仿真电子教案_matlab在通信中的应用(二进制基带系统).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)MATLAB与通信仿真电子教案_matlab在通信中的应用(模拟信号的数字传输).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)MATLAB与通信仿真电子教案_matlab在通信中的应用(模拟调制系统).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)MATLAB与通信仿真电子教案_第2章 matlab语言入门.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)MATLAB与通信仿真电子教案_第3章 图形处理与simulink仿真.ppt

- 《通信原理实验》课程电子教案(PPT讲稿)MATLAB与通信仿真电子教案_第1章 matlab基础知识.ppt

- 《通信原理实验》课程电子教案(讲稿)MATLAB与通信仿真(英文)Chapter 1 Basic Matlab.doc

- 《通信原理实验》课程电子教案(PPT讲稿)MATLAB与通信仿真(英文)Chapter 2 Analog Modulation(AM,Amplitude Modulation).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)MATLAB与通信仿真(英文)Chapter 2 Analog Modulation(Conventional AM).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)MATLAB与通信仿真(英文)Chapter 2 Analog Modulation(SSB – AM).ppt

- 《通信原理实验》课程电子教案(讲稿)MATLAB与通信仿真(英文)Chapter 7 Spread Spectrum Communication Systems.doc

- 《通信原理实验》课程电子教案(PPT讲稿)MATLAB与通信仿真(英文)Chapter 2 Analog Modulation(Frequency Modulation、Phase Modulation).ppt

- 《通信原理实验》课程电子教案(PPT讲稿)MATLAB与通信仿真(英文)Chapter 2 Transmitters and Receivers.ppt