上海交通大学:《数字集成电路 Digital Integrated Circuit》课程教学资源(课程实验)HSPICE SIMULATION

DIC 2014 lab1 TA:Pengzhi Chu MicroE@SJTU HSPICE SIMULATION

HSPICE SIMULATION DIC_2014_lab1 TA: Pengzhi Chu MicroE@SJTU

Outline Introduction to Hspice Hspice simulation lab1 Lab Report

Outline Introduction to Hspice Hspice simulation_lab1 Lab Report

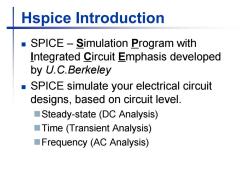

Hspice Introduction SPICE-Simulation Program with Integrated Circuit Emphasis developed by U.C.Berkeley SPICE simulate your electrical circuit designs,based on circuit level. Steady-state (DC Analysis) Time (Transient Analysis) Frequency (AC Analysis) ■

Hspice Introduction SPICE – Simulation Program with Integrated Circuit Emphasis developed by U.C.Berkeley SPICE simulate your electrical circuit designs, based on circuit level. Steady-state (DC Analysis) Time (Transient Analysis) Frequency (AC Analysis)

Hspice Introduction HSPICE Models Analog/RF Custom digital Standard cell Signal integrity

Hspice Introduction

Basic Netlist Structure Title ■Device models or ■.SUBCKT ■.OPTIONS ■Netlist (conditions for ■.ENDS simulation) ☐Output format ☐Analysis&temp. ■.ALTER ☐.lc(initial state) ■Netlist ■.GLOBAL ■.END ■.PARAM ■Source ■Netlist

Basic Netlist Structure Title * or $ .OPTIONS (conditions for simulation) Analysis & temp. .IC (initial state) .GLOBAL .PARAM Source Netlist Device models .SUBCKT Netlist .ENDS Output format .ALTER Netlist .END

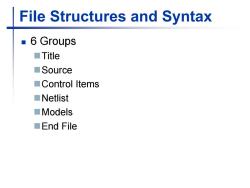

File Structures and Syntax 6 Groups ■Title ■Source ■Control Items ■Netlist ■Models End File

File Structures and Syntax 6 Groups Title Source Control Items Netlist Models End File

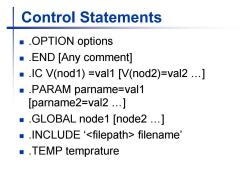

Control Statements ■.OPTION options ■.END[Any comment] .IC V(nod1)=val1 [V(nod2)=val2 ... ■.PARAM parname:=val1 [parname2=val2 ... .GLOBAL node1 [node2 ... .INCLUDE 'filename .TEMP temprature

Control Statements .OPTION options .END [Any comment] .IC V(nod1) =val1 [V(nod2)=val2 …] .PARAM parname=val1 [parname2=val2 …] .GLOBAL node1 [node2 …] .INCLUDE „ filename‟ .TEMP temprature

Library Statement LIB library call statement ■.lib‘filename'entryname .endl entryname .INCLUDE statement

Library Statement .LIB library call statement .lib „filename‟ entryname .endl entryname .INCLUDE statement

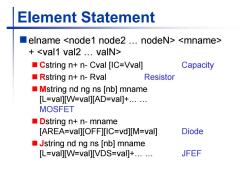

Element Statement elname Cstring n+n-Cval [IC=Vval] Capacity ■Rstring n+n-Rval Resistor Mstring nd ng ns [nb]mname [L=val][W=val][AD=val]+...... MOSFET Dstring n+n-mname [AREA=val][OFF][IC=vd][M=val] Diode Jstring nd ng ns [nb]mname [L=val][W=val][VDS=val]+...... JFEF

Element Statement elname + Cstring n+ n- Cval [IC=Vval] Capacity Rstring n+ n- Rval Resistor Mstring nd ng ns [nb] mname [L=val][W=val][AD=val]+… … MOSFET Dstring n+ n- mname [AREA=val][OFF][IC=vd][M=val] Diode Jstring nd ng ns [nb] mname [L=val][W=val][VDS=val]+… … JFEF

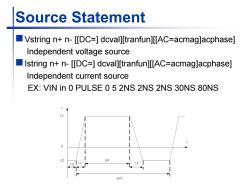

Source Statement Vstring n+n-[[DC=]dcval][tranfun][[AC=acmag]acphase] Independent voltage source Istring n+n-[[DC=]dcval][tranfun][[AC=acmag]acphase] Independent current source EX:VIN in 0 PULSE 0 5 2NS 2NS 2NS 30NS 80NS vl 0 v2 pw td tr per

Source Statement Vstring n+ n- [[DC=] dcval][tranfun][[AC=acmag]acphase] Independent voltage source Istring n+ n- [[DC=] dcval][tranfun][[AC=acmag]acphase] Independent current source EX: VIN in 0 PULSE 0 5 2NS 2NS 2NS 30NS 80NS

按次数下载不扣除下载券;

注册用户24小时内重复下载只扣除一次;

顺序:VIP每日次数-->可用次数-->下载券;

- 上海交通大学:《数字集成电路 Digital Integrated Circuit》课程教学资源(讲义)Introduction(Semiconductor processing).pdf

- 上海交通大学:《电路基础》课程教学资源(PPT课件)第二章 电路分析的基本方法 §2.8 回路分析法 §2.9 节点分析法.ppt

- 上海交通大学:《通信基本电路》课程教学资源(参考资料)Fundamental of Communication Circuits Lecture 1 Introduction.ppt

- 上海交通大学:《电路基础》课程教学资源(PPT课件)第三章 电路定理 §3.4 互易定理.ppt

- 上海交通大学:《电路基础》课程教学资源(PPT课件)第三章 电路定理 §3.3 戴维宁定理和诺顿定理.ppt

- 上海交通大学:《电路基础》课程教学资源(PPT课件)第三章 电路定理 §3.1 替代定理 §3.2 叠加定理.ppt

- 上海交通大学:《电路基础》课程教学资源(PPT课件)第二章 电路分析的基本方法 §2.14 二端口电路的端口特性分析 §2.15 电路的对偶性.ppt

- 上海交通大学:《电路基础》课程教学资源(PPT课件)第二章 电路分析的基本方法 §2.14 二端口电路的端口特性分析.ppt

- 上海交通大学:《电路基础》课程教学资源(PPT课件)第二章 电路分析的基本方法 §2.13 一端口电路的端口特性分析 §2.14 二端口电路的端口特性分析.ppt

- 上海交通大学:《电路基础》课程教学资源(PPT课件)第二章 电路分析的基本方法 §2.9 节点分析法系统方法 §2.10 网孔分析法 §2.11 基本回路分析法 §2.12 基本割集分析法.ppt

- 上海交通大学:《电路基础》课程教学资源(PPT课件)第二章 电路分析的基本方法 §2.7 具有对称性质的电路.ppt

- 上海交通大学:《电路基础》课程教学资源(PPT课件)第二章 电路分析的基本方法(§2.1 - §2.6).ppt

- 上海交通大学:《电路基础》课程教学资源(PPT课件)第一章 基本概念和基本规律 §1.4.3 受控电源 §1.4.4 运算放大器 §1.4.5 理想变压器 §1.4.6 回转器 §1.4.7 负转换器.ppt

- 上海交通大学:《电路基础》课程教学资源(PPT课件)第一章 基本概念和基本规律 §1.4.2 独立电源 §1.4.2 几种典型的独立源信号波形及其符号.ppt

- 上海交通大学:《电路基础》课程教学资源(PPT课件)第一章 基本概念和基本规律 §1.4.1 电阻元件及其约束方程 §1.4.1 功率和能量.ppt

- 上海交通大学:《电路基础》课程教学资源(PPT课件)第一章 基本概念和基本规律 §1.3.1 基尔霍夫定律 §1.3.2 基尔霍夫定律 §1.3.3 从网络到图 §1.3.4 KCL、KVL的矩阵形式 §1.3.5 特勒根定理.ppt

- 上海交通大学:《电路与电子技术》课程教学资源(课件讲稿)数字电子技术——触发器和时序逻辑电路.pdf

- 上海交通大学:《电路与电子技术》课程教学资源(课件讲稿)数字电子技术——门电路和组合逻辑电路.pdf

- 上海交通大学:《电路与电子技术》课程教学资源(课件讲稿)常用半导体器件.pdf

- 上海交通大学:《电路与电子技术》课程教学资源(课件讲稿)多级放大电路.ppt

- 上海交通大学:《数字集成电路 Digital Integrated Circuit》课程教学资源(课程实验)Lab #1:HSPICE Simulation.pdf

- 《数字集成电路 Digital Integrated Circuit》课程教学资源(阅读资料)IC testing_3D DFT challenges and solutions.pdf

- 《数字集成电路 Digital Integrated Circuit》课程教学资源(阅读资料)IC testing_An introduction to IC testing.pdf

- 《数字集成电路 Digital Integrated Circuit》课程教学资源(阅读资料)IC testing_DESIGN AND TESTING OF COMBINATIONAL LOGIC CIRCUITS USING BUILT IN SELF TEST SCHEME FOR FPGAs.pdf

- 《数字集成电路 Digital Integrated Circuit》课程教学资源(阅读资料)IC testing_Design, Manufacturing & Test of Integrated Circuits in the Nanotechnology Era.pdf

- 《数字集成电路 Digital Integrated Circuit》课程教学资源(阅读资料)IC testing_IC design-for-test and testability features.pdf

- 《数字集成电路 Digital Integrated Circuit》课程教学资源(阅读资料)IC testing_Novel Applications of Deep Learning Hidden Features for Adaptive Testing.pdf

- 《微电子学概论》课程教学资源:用十分鐘瞭解《圖靈獎得主》的學術貢獻.pdf

- 上海交通大学:《微电子学概论》课程教学资源_图灵奖下的人类智力延伸——-计算、集成电路及应用.pdf

- 《Electronics Lab》课程教学资源:Lab 01 Combinational Logic.pdf

- 《Electronics Lab》课程教学资源:Lab 11 OBJECTIVES.pdf

- 《Electronics Lab》课程教学资源:Lab 12&13 Feedback amplifiers.pdf

- 《Electronics Lab》课程教学资源:Lab 02 Decoder and demultiplexer.pdf

- 《Electronics Lab》课程教学资源:Lab 03 Edged-triggered Flip-Flops.pdf

- 《Electronics Lab》课程教学资源:Lab 04 counters.pdf

- 《Electronics Lab》课程教学资源:Lab 05 & 06 op-amp:adder、Integrator & Differentiator.pdf

- 《Electronics Lab》课程教学资源:Lab 07 & 08 filter、Function Generator.pdf

- 《Electronics Lab》课程教学资源:Lab 09 & 10 Transistor Amplifier.pdf

- 上海交通大学:《通信原理与实验 Principles and Experiments of Communications》课程教学资源(PPT讲稿)Intro.ppt

- 《通信原理与实验 Principles and Experiments of Communications》课程参考书:John G. Proakis Masoud Salehi《Fundamentals of Communication Systems》(Second Edition).pdf