电子科技大学:《ASIC设计 Application Specific Integrated Circuit Design(ASIC)》课程教学资源(课件讲稿)Topic 2 FPGA Design with Verilog(Supplementary)

Topic2:FPGA Design with Verilog FPGA Design Method Design flow tools Deign Model of Verilog HDL Design style of Verilog HDL Design Examples 。RTL level design Components of Datapath Components of Controller Supplementary ·Synthesizable 。Some experiences 。Other syntax rules 2021/1/13 ASIC Design,by Yan Bo 3

ASIC Design, by Yan Bo Topic2: FPGA Design with Verilog FPGA Design Method Design flow & tools Deign Model of Verilog HDL Design style of Verilog HDL Design Examples • RTL level design • Components of Datapath • Components of Controller Supplementary • Synthesizable • Some experiences • Other syntax rules 2021/1/13 3

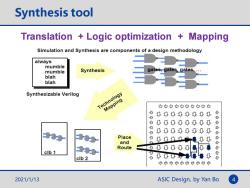

Synthesis tool Translation Logic optimization Mapping Simulation and Synthesis are components of a design methodology always mumble mumble Synthesis gates,gates,gates, blah blah Synthesizable Verilog Technology Mapping 白白白白白白白白白白 800000000 0中中中中中中中中 0 中中中中中中中中 Place and 00n是09 0 Route clb1 clb2 中中中中中中中单中中 2021/1/13 ASIC Design,by Yan Bo

ASIC Design, by Yan Bo Synthesis tool 2021/1/13 4 Translation + Logic optimization + Mapping

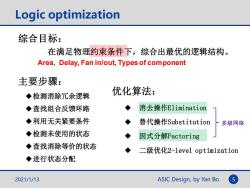

Logic optimization 综合目标: 在满足物理约束条件下,综合出最优的逻辑结构。 Area,Delay,Fan in/out,Types of component 主要步骤: 优化算法: ◆检测消除冗余逻辑 ◆查找组合反馈环路 消去操作Elimination ◆利用无关紧要条件 替代操作Substitution ,上多级网络 ◆检测未使用的状态 因式分解Factoring ◆查找消除等价的状态 二级优化2-level optimization ◆进行状态分配 2021/1/13 ASIC Design,by Yan Bo 5

ASIC Design, by Yan Bo Logic optimization 2021/1/13 5 主要步骤: ◆检测消除冗余逻辑 ◆查找组合反馈环路 ◆利用无关紧要条件 ◆检测未使用的状态 ◆查找消除等价的状态 ◆进行状态分配 综合目标: 在满足物理约束条件下,综合出最优的逻辑结构。 Area, Delay, Fan in/out, Types of component 优化算法: ◆ 消去操作Elimination ◆ 替代操作Substitution ◆ 因式分解Factoring ◆ 二级优化2-level optimization 多级网络

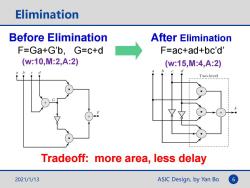

Elimination Before Elimination After Elimination F=Ga+G'b,G=c+d F=ac+ad+bc'd' w:10,M:2,A:2) (w:15,M:4,A:2) b c a Two-level Tradeoff:more area,less delay 2021/1/13 ASIC Design,by Yan Bo 6

ASIC Design, by Yan Bo Elimination 2021/1/13 6 After Elimination F=ac+ad+bc’d’ Before Elimination F=Ga+G’b, G=c+d (w:10,M:2,A:2) (w:15,M:4,A:2) Tradeoff: more area, less delay

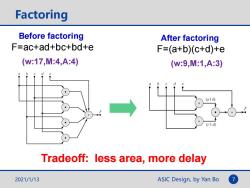

Factoring Before factoring After factoring F=ac+ad+bc+bd+e F=(a+b)(c+d)+e w:17,M:4,A:4) (W:9,M:1,A:3) b (a1b) (c1d) Tradeoff:less area,more delay 2021/1/13 ASIC Design,by Yan Bo 7

ASIC Design, by Yan Bo Factoring 2021/1/13 7 Tradeoff: less area, more delay After factoring F=(a+b)(c+d)+e Before factoring F=ac+ad+bc+bd+e (w:17,M:4,A:4) (w:9,M:1,A:3)

Topic2:FPGA Design with Verilog FPGA Design Method Design flow tools Deign Model of Verilog HDL Design style of Verilog HDL Design Examples 。RTL level design Components of Datapath Components of Controller Supplementary 。Synthesizable ·Some experiences 。Other syntax rules 2021/1/13 ASIC Design,by Yan Bo 8

ASIC Design, by Yan Bo Topic2: FPGA Design with Verilog FPGA Design Method Design flow & tools Deign Model of Verilog HDL Design style of Verilog HDL Design Examples • RTL level design • Components of Datapath • Components of Controller Supplementary • Synthesizable • Some experiences • Other syntax rules 2021/1/13 8

Some experiences >Balance architecture Share resources Gated signal >Assignment statement Accident Intentional Latch 2021/1/13 ASIC Design,by Yan Bo 9

ASIC Design, by Yan Bo Some experiences 2021/1/13 9 ➢ Balance architecture ➢ Share resources ➢ Gated signal ➢Assignment statement ➢ Accident / Intentional Latch

Some experiences Balance architecture Share resources Gated signal >Assignment statement Accident Intentional Latch 2021/1/13 ASIC Design,by Yan Bo 10

ASIC Design, by Yan Bo Some experiences 2021/1/13 10 ➢ Balance architecture ➢ Share resources ➢ Gated signal ➢Assignment statement ➢ Accident / Intentional Latch

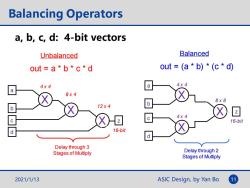

Balancing Operators a,b,c,d:4-bit vectors Unbalanced Balanced out a b c d out =(a b)*(c d) a 4X4 a 4X4 8X4 8X8 12x4 回 4X4 16-bit 16-bit Delay through 3 Stages of Multiply Delay through 2 Stages of Multiply 2021/1/13 ASIC Design,by Yan Bo 11

ASIC Design, by Yan Bo Balancing Operators a, b, c, d: 4-bit vectors out = a * b * c * d X a b X c X d z X a b out = (a * b) * (c * d) X c d X z Unbalanced Balanced 4 x 4 8 x 4 12 x 4 16-bit 4 x 4 4 x 4 8 x 8 16-bit Delay through 3 Stages of Multiply Delay through 2 Stages of Multiply 2021/1/13 11

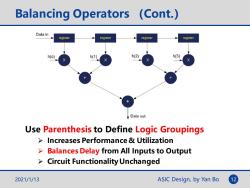

Balancing Operators (Cont.) Data in register register register register h(o) h(1) h(2) h(3) Data out Use Parenthesis to Define Logic Groupings Increases Performance Utilization >Balances Delay from All Inputs to Output Circuit Functionality Unchanged 2021/1/13 ASIC Design,by Yan Bo 12

ASIC Design, by Yan Bo Balancing Operators (Cont.) 2021/1/13 12 Use Parenthesis to Define Logic Groupings ➢ Increases Performance & Utilization ➢ Balances Delay from All Inputs to Output ➢ Circuit Functionality Unchanged

按次数下载不扣除下载券;

注册用户24小时内重复下载只扣除一次;

顺序:VIP每日次数-->可用次数-->下载券;

- 电子科技大学:《ASIC设计 Application Specific Integrated Circuit Design(ASIC)》课程教学资源(课件讲稿)Topic 2 FPGA Design with Verilog(FPGA Design Method、Design Examples).pdf

- 电子科技大学:《ASIC设计 Application Specific Integrated Circuit Design(ASIC)》课程教学资源(课件讲稿)Topic1 Introduction(About Our Course).pdf

- 电子科技大学:《ASIC设计 Application Specific Integrated Circuit Design(ASIC)》课程教学资源(课件讲稿)Topic 1 Introduction(About ASIC Design).pdf

- 电子科技大学:《ASIC设计 Application Specific Integrated Circuit Design(ASIC)》课程教学资源(课件讲稿)Topic 1 Introduction(About IC technology).pdf

- 广东海洋大学:《数字信号处理 Digital Signal Processing》课程教学资源(电子教案).doc

- 电子科技大学:《贝叶斯学习与随机矩阵及在无线通信中的应用 BI-RM-AWC》课程教学资源(学习资料)随机矩阵补充材料 Analysis of neural networks - a random matrix approach.pdf

- 电子科技大学:《贝叶斯学习与随机矩阵及在无线通信中的应用 BI-RM-AWC》课程教学资源(学习资料)贝叶斯学习补充材料.pdf

- 电子科技大学:《贝叶斯学习与随机矩阵及在无线通信中的应用 BI-RM-AWC》课程教学资源(课件讲稿)09 Sparse Signal Recovery.pdf

- 电子科技大学:《贝叶斯学习与随机矩阵及在无线通信中的应用 BI-RM-AWC》课程教学资源(课件讲稿)08 Linear Regression.pdf

- 《贝叶斯学习与随机矩阵及在无线通信中的应用 BI-RM-AWC》课程教学资源(学习资料)Random Matrix Theory and Wireless Communications.pdf

- 电子科技大学:《贝叶斯学习与随机矩阵及在无线通信中的应用 BI-RM-AWC》课程教学资源(课件讲稿)05 Free Probability.pdf

- 电子科技大学:《贝叶斯学习与随机矩阵及在无线通信中的应用 BI-RM-AWC》课程教学资源(课件讲稿)07 Analysis of neural networks - a random matrix approach.pdf

- 电子科技大学:《贝叶斯学习与随机矩阵及在无线通信中的应用 BI-RM-AWC》课程教学资源(课件讲稿)06 Non-asymptotic Analysis for Large Random Matrix.pdf

- 电子科技大学:《贝叶斯学习与随机矩阵及在无线通信中的应用 BI-RM-AWC》课程教学资源(课件讲稿)04 Asymptotic Spectrum Theorems(4/4).pdf

- 电子科技大学:《贝叶斯学习与随机矩阵及在无线通信中的应用 BI-RM-AWC》课程教学资源(课件讲稿)04 Asymptotic Spectrum Theorems(3/4).pdf

- 电子科技大学:《贝叶斯学习与随机矩阵及在无线通信中的应用 BI-RM-AWC》课程教学资源(课件讲稿)04 Asymptotic Spectrum Theorems(2/4).pdf

- 《贝叶斯学习与随机矩阵及在无线通信中的应用 BI-RM-AWC》课程教学资源(文献书籍)An Introduction to Random Matrices(Greg W. Anderson、Alice Guionnet).pdf

- 电子科技大学:《贝叶斯学习与随机矩阵及在无线通信中的应用 BI-RM-AWC》课程教学资源(课件讲稿)04 Asymptotic Spectrum Theorems(1/4).pdf

- 电子科技大学:《贝叶斯学习与随机矩阵及在无线通信中的应用 BI-RM-AWC》课程教学资源(课件讲稿)03 Transforms.pdf

- 电子科技大学:《贝叶斯学习与随机矩阵及在无线通信中的应用 BI-RM-AWC》课程教学资源(课件讲稿)02 Types of Matrices and Local Non-Asymptotic Results.pdf

- 电子科技大学:《ASIC设计 Application Specific Integrated Circuit Design(ASIC)》课程教学资源(课件讲稿)Topic 3 Verification and Test.pdf

- 电子科技大学:《ASIC设计 Application Specific Integrated Circuit Design(ASIC)》课程教学资源(课件讲稿)Topic 4 VLSI for DSP.pdf

- 电子科技大学:《高等数字集成电路设计 Advanced Digital Integrated Circuits Design》课程教学资源(教学大纲,负责人:贺雅娟).pdf

- 电子科技大学:《高等数字集成电路设计 Advanced Digital Integrated Circuits Design》课程教学资源(课件讲稿)Lecture 1 Introduction & The Fabrics.pdf

- 电子科技大学:《模拟集成电路分析与设计 Analysis and Design of Analog Integrated Circuit》课程教学资源(教学大纲,负责人:罗萍).pdf

- 电子科技大学:《模拟集成电路分析与设计 Analysis and Design of Analog Integrated Circuit》课程教学资源(课件讲稿)Chapter 01 Introduction、Models and comparison of integrated-circuit active devices.pdf

- 电子科技大学:《模拟集成电路分析与设计 Analysis and Design of Analog Integrated Circuit》课程教学资源(课件讲稿)Chapter 02 Amplifiers, source followers and cascodes.pdf

- 川北医学院:《模拟电子技术》课程电子教案(课件讲稿)第四章 集成运算放大器 integrated operational amplifier.pdf

- 川北医学院:《模拟电子技术》课程电子教案(课件讲稿)第四章 双极结型三极管及放大电路基础.pdf

- 《信号与系统》课程教学资源(课件讲稿)第2章 线性时不变系统的时域分析.pdf

- 川北医学院:《模拟电子技术》课程电子教案(课件讲稿)第五章 场效应管放大电路.pdf

- 川北医学院:《模拟电子技术》课程电子教案(课件讲稿)第三章 二极管及其基本电路.pdf

- 《电子技术基础》课程教学资源(课件讲稿)第五章 振荡电路 oscillator.pdf

- 《单片机原理及应用》课程教学资源(课件讲稿)第7章 并行扩展技术.pdf

- 聊城大学:《信息与系统》课程教学资源(课件讲稿)第一章 绪论.pdf

- 聊城大学:《信息与系统》课程教学资源(课件讲稿)第二章 连续系统的时域分析.pdf

- 聊城大学:《信息与系统》课程教学资源(课件讲稿)第三章 傅里叶变换(PPT课件).ppt

- 聊城大学:《信息与系统》课程教学资源(课件讲稿)第四章 拉普拉斯变换、连续时间系统的S域分析.pdf

- 聊城大学:《信息与系统》课程教学资源(课件讲稿)第七章 离散时间系统的时域分析.pdf

- 聊城大学:《信息与系统》课程教学资源(课件讲稿)第八章 离散时间系统的z域分析.pdf