中国地质大学(武汉):《EDA技术基础与实践(Electronic Design Automation)》课程教学资源(实验内容)实验十一 交通灯实验

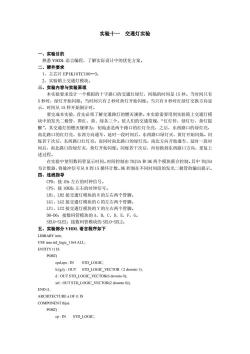

实验十一 交通灯实验 一、实验目的 熟悉VHDL语言编程,了解实际设计中的优化方案。 二、硬件要求 1、主芯片EP1K10TC100一3: 2、实验箱上交通灯模块。 三、实验内容与实验原理 本实验要求设计一个模拟的十字路口的交通红绿灯,间隔的时间是15秒。当时间只有 5秒时,绿灯开始闪烁:当时间只有2秒时黄灯开始闪烁。当只有0秒时红绿灯交换方向显 示,时间从15秒开始倒计时。 要完成本实验,首先必须了解交通路灯的燃灭规律。本实验需要用到实验箱上交通灯模 块中的发光二极管,即红、黄、绿各三个。依人们的交通常规,“红灯停,绿灯行,黄灯提 醒”。其交通灯的燃灭规律为:初始态是两个路口的红灯全亮,之后,东西路口的绿灯亮, 南北路口的红灯亮,东西方向通车,延时一段时间后,东西路口绿灯灭,黄灯开始闪烁。闪 烁若干次后,东西路口红灯亮,而同时南北路口的绿灯亮,南北方向开始通车,延时一段时 间后,南北路口的绿灯灭,黄灯开始闪烁。闪烁若干次后,再切换到东西路口方向,重复上 述过程。 在实验中使用数码管显示时间。时间控制由TBJSA和DK两个模块联合控制。其中TBJSA 为计数器,将脉冲信号从0到15循环计数。DK控制在不同时间段的发光二极管的输出提示。 四、连线指导 CPD:接1Hz左右的时钟信号。 CPS:接10KHz左右的时钟信号。 LR1、LR2接交通灯模块的R的左右两个管脚。 LG1、LG2接交通灯模块的G的左右两个管脚。 LY1、LY2接交通灯模块的Y的左右两个管脚。 D0-D6:接数码管模块的A,B,C,D,E,F,G。 SEL0-SLE2:接数码管模块的SEL0-SEL2。 五、实验部分VHDL语言程序如下 LIBRARY ieee; USE ieee.std_logic_1164.ALL; ENTITY tI IS PORT( cpd,cps IN STD LOGIC: Ir,lg,ly:OUT STD_LOGIC_VECTOR (2 downto 1); d:OUT STD LOGIC VECTOR(6 downto 0); sel:OUT STD LOGIC VECTOR(2 downto 0)); END tl; ARCHITECTURE a OF t1 IS COMPONENT tbisa PORT( cp:IN STD LOGIC;

实验十一 交通灯实验 一、实验目的 熟悉 VHDL 语言编程,了解实际设计中的优化方案。 二、硬件要求 1、主芯片 EP1K10TC100—3; 2、实验箱上交通灯模块。 三、实验内容与实验原理 本实验要求设计一个模拟的十字路口的交通红绿灯,间隔的时间是 15 秒。当时间只有 5 秒时,绿灯开始闪烁;当时间只有 2 秒时黄灯开始闪烁。当只有 0 秒时红绿灯交换方向显 示,时间从 15 秒开始倒计时。 要完成本实验,首先必须了解交通路灯的燃灭规律。本实验需要用到实验箱上交通灯模 块中的发光二极管,即红、黄、绿各三个。依人们的交通常规,“红灯停,绿灯行,黄灯提 醒”。其交通灯的燃灭规律为:初始态是两个路口的红灯全亮,之后,东西路口的绿灯亮, 南北路口的红灯亮,东西方向通车,延时一段时间后,东西路口绿灯灭,黄灯开始闪烁。闪 烁若干次后,东西路口红灯亮,而同时南北路口的绿灯亮,南北方向开始通车,延时一段时 间后,南北路口的绿灯灭,黄灯开始闪烁。闪烁若干次后,再切换到东西路口方向,重复上 述过程。 在实验中使用数码管显示时间。时间控制由 TBJSA 和 DK 两个模块联合控制。其中 TBJSA 为计数器,将脉冲信号从 0 到 15 循环计数。DK 控制在不同时间段的发光二极管的输出提示。 四、连线指导 CPD:接 1Hz 左右的时钟信号。 CPS:接 10KHz 左右的时钟信号。 LR1、LR2 接交通灯模块的 R 的左右两个管脚。 LG1、LG2 接交通灯模块的 G 的左右两个管脚。 LY1、LY2 接交通灯模块的 Y 的左右两个管脚。 D0-D6:接数码管模块的 A,B,C,D,E,F,G。 SEL0-SLE2:接数码管模块的 SEL0-SEL2。 五、实验部分 VHDL 语言程序如下 LIBRARY ieee; USE ieee.std_logic_1164.ALL; ENTITY t1 IS PORT( cpd,cps : IN STD_LOGIC; lr,lg,ly : OUT STD_LOGIC_VECTOR(2 downto 1); d : OUT STD_LOGIC_VECTOR(6 downto 0); sel : OUT STD_LOGIC_VECTOR(2 downto 0)); END t1; ARCHITECTURE a OF t1 IS COMPONENT tbjsa PORT( cp : IN STD_LOGIC;

q:OUT STD_LOGIC_VECTOR(4 downto 0)); END COMPONENT: COMPONENT tbjsb PORT( cp:IN STD LOGIC; q:OUT STD LOGIC_VECTOR(2 downto 0)): END COMPONENT: COMPONENT dk PORT( cp IN STD_LOGIC; si:IN STD LOGIC VECTOR(4 downto 1): Ir,lg.ly:OUT STD_LOGIC_VECTOR(4 downto 1)): END COMPONENT: COMPONENT sx PORT( sj:IN STD LOGIC VECTOR(3 downto 0); kz IN STD_LOGIC; d:OUT STD LOGIC VECTOR(6 downto 0)): END COMPONENT: SIGNAL nsj STD_LOGIC_VECTOR(4 downto 0); SIGNAL nwk:STD LOGIC VECTOR(2 downto 0); BEGIN 1 a:tbjsa PORT MAP(cpd,nsj); 1_b:tbjsb PORT MAP(cps,nwk); 1_c:dk PORT MAP(cpd,nsj(4 downto 1),Ir,Ig,ly); 1_d:sx PORT MAP(nsj(3 downto 0),nwk(0),d); sel <nwk; END a; LIBRARY ieee; USE ieee.std_logic_1164.ALL; ENTITY sx IS PORT( sj IN STD_LOGIC_VECTOR(3 downto 0); kz IN STD LOGIC: d:OUT STD_LOGIC_VECTOR(6 downto 0)); END sx; ARCHITECTURE a OF sx IS SIGNAL nsjh,nsjl STD_LOGIC_VECTOR(6 downto 0); BEGIN with sj select nsjh<="0000110"when"1111

q : OUT STD_LOGIC_VECTOR(4 downto 0)); END COMPONENT; COMPONENT tbjsb PORT( cp : IN STD_LOGIC; q : OUT STD_LOGIC_VECTOR(2 downto 0)); END COMPONENT; COMPONENT dk PORT( cp : IN STD_LOGIC; sj : IN STD_LOGIC_VECTOR(4 downto 1); lr,lg,ly : OUT STD_LOGIC_VECTOR(4 downto 1)); END COMPONENT; COMPONENT sx PORT( sj : IN STD_LOGIC_VECTOR(3 downto 0); kz : IN STD_LOGIC; d : OUT STD_LOGIC_VECTOR(6 downto 0)); END COMPONENT; SIGNAL nsj : STD_LOGIC_VECTOR(4 downto 0); SIGNAL nwk : STD_LOGIC_VECTOR(2 downto 0); BEGIN l_a: tbjsa PORT MAP (cpd,nsj); l_b: tbjsb PORT MAP (cps,nwk); l_c: dk PORT MAP (cpd,nsj(4 downto 1),lr,lg,ly); l_d: sx PORT MAP (nsj(3 downto 0),nwk(0),d); sel <= nwk; END a; LIBRARY ieee; USE ieee.std_logic_1164.ALL; ENTITY sx IS PORT( sj : IN STD_LOGIC_VECTOR(3 downto 0); kz : IN STD_LOGIC; d : OUT STD_LOGIC_VECTOR(6 downto 0)); END sx; ARCHITECTURE a OF sx IS SIGNAL nsjh,nsjl : STD_LOGIC_VECTOR(6 downto 0); BEGIN with sj select nsjh <= "0000110" when "1111", ……

"0000000"when others; with sj select nsjl="01111l1"when"0000", "1101101"when"1111" "0000000"when others; with kz select d<=nsjl when'1', nsjh when'0', "0000000"when others; END a; LIBRARY ieee; USE ieee.std_logic_1164.ALL; ENTITY dk IS PORT( cp IN STD_LOGIC: sj:IN STD LOGIC VECTOR(4 downto 1): Ir,lg,ly:OUT STD LOGIC VECTOR(4 downto 1)); END dk: ARCHITECTURE a OF dk IS SIGNAL ra,rb,ga,gb,ya,yb:STD LOGIC; BEGIN ra<=si(4): rb<=not sj(4)方 ga<=(not sj(4))and(sj(3)or(sj(2)and sj(1))or((sj(2)xor sj(1))and cp)); gb <si(4)and(si(3)or(si(2)and sj(1))or((si(2)xor si(1))and cp)); ya<=(not sj(4))and(not(sj(3)or sj(2)or sj(1))); yb <sj(4)and(not(sj(3)or sj(2)or sj(1))); Ir(1)<=ra; lr(2)<=rb: lg(1)<=ga; 1g(2)<=gb, ly(1)<=ya; y(2)<=yb: END a; 六、实验报告 1、仔细分析该实验程序,可以试着将其分成几个基本模块,以备将来设计时随时调用: 2、仔细分析该实验程序,看是否将其优化: 3、可以仔细观察街道上的交通实况,根据实际情况或假想情况调整设计思路

"0000000" when others; with sj select nsjl <= "0111111" when "0000", …… "1101101" when "1111", "0000000" when others; with kz select d <= nsjl when '1', nsjh when '0', "0000000" when others; END a; LIBRARY ieee; USE ieee.std_logic_1164.ALL; ENTITY dk IS PORT( cp : IN STD_LOGIC; sj : IN STD_LOGIC_VECTOR(4 downto 1); lr,lg,ly : OUT STD_LOGIC_VECTOR(4 downto 1)); END dk; ARCHITECTURE a OF dk IS SIGNAL ra,rb,ga,gb,ya,yb : STD_LOGIC; BEGIN ra <= sj(4); rb <= not sj(4); ga <= (not sj(4))and(sj(3)or(sj(2)and sj(1))or((sj(2)xor sj(1))and cp)); gb <= sj(4)and(sj(3)or(sj(2)and sj(1))or((sj(2)xor sj(1))and cp)); ya <= (not sj(4))and(not(sj(3)or sj(2)or sj(1))); yb <= sj(4)and(not(sj(3)or sj(2)or sj(1))); lr(1) <= ra; lr(2) <= rb; lg(1) <= ga; lg(2) <= gb; ly(1) <= ya; ly(2) <= yb; END a; 六、实验报告 1、 仔细分析该实验程序,可以试着将其分成几个基本模块,以备将来设计时随时调用; 2、 仔细分析该实验程序,看是否将其优化; 3、 可以仔细观察街道上的交通实况,根据实际情况或假想情况调整设计思路

按次数下载不扣除下载券;

注册用户24小时内重复下载只扣除一次;

顺序:VIP每日次数-->可用次数-->下载券;

- 中国地质大学(武汉):《EDA技术基础与实践(Electronic Design Automation)》课程教学资源(实验内容)实验十 VGA彩条信号发生器实验.pdf

- 中国地质大学(武汉):《EDA技术基础与实践(Electronic Design Automation)》课程教学资源(实验内容)实验九 键盘扫描显示实验.pdf

- 中国地质大学(武汉):《EDA技术基础与实践(Electronic Design Automation)》课程教学资源(实验内容)实验八 AD转换实验.pdf

- 中国地质大学(武汉):《EDA技术基础与实践(Electronic Design Automation)》课程教学资源(实验内容)实验七 梁祝音乐演奏实验.pdf

- 中国地质大学(武汉):《EDA技术基础与实践(Electronic Design Automation)》课程教学资源(实验内容)实验六 数字钟实验.pdf

- 中国地质大学(武汉):《EDA技术基础与实践(Electronic Design Automation)》课程教学资源(实验内容)实验四 扫描显示电路的驱动.pdf

- 中国地质大学(武汉):《EDA技术基础与实践(Electronic Design Automation)》课程教学资源(实验内容)实验五 计数器及时序电路.pdf

- 中国地质大学(武汉):《EDA技术基础与实践(Electronic Design Automation)》课程教学资源(实验内容)实验二 组合逻辑设计.pdf

- 中国地质大学(武汉):《EDA技术基础与实践(Electronic Design Automation)》课程教学资源(实验内容)实验三 触发器功能模拟.pdf

- 中国地质大学(武汉):《EDA技术基础与实践(Electronic Design Automation)》课程教学资源(实验内容)实验一 实验箱介绍及软件安装.pdf

- 中国地质大学(武汉):《信号与系统 Signals and Systems》课程教学资源(课件讲稿)第八章 Z变换.pdf

- 中国地质大学(武汉):《信号与系统 Signals and Systems》课程教学资源(课件讲稿)第七章 离散信号、离散系统.pdf

- 中国地质大学(武汉):《信号与系统 Signals and Systems》课程教学资源(课件讲稿)第六章 傅里叶变换的应用.pdf

- 中国地质大学(武汉):《信号与系统 Signals and Systems》课程教学资源(课件讲稿)第五章 拉普拉斯变换.pdf

- 中国地质大学(武汉):《信号与系统 Signals and Systems》课程教学资源(课件讲稿)第四章 信号的谱表示.pdf

- 中国地质大学(武汉):《信号与系统 Signals and Systems》课程教学资源(课件讲稿)第三章 泛函分析初步.pdf

- 中国地质大学(武汉):《信号与系统 Signals and Systems》课程教学资源(课件讲稿)第二章 LTI连续时间系统的时域分析.pdf

- 中国地质大学(武汉):《信号与系统 Signals and Systems》课程教学资源(课件讲稿)第一章 绪论.pdf

- 中国地质大学(武汉):《信号与系统 Signals and Systems》课程教学资源(课件讲稿)概要.pdf

- 人民邮电出版社:图灵电子与电气工程丛书《锁相技术 Phase-Locked Loops Technology》教材PDF电子书(第3版,共十七章).pdf

- 中国地质大学(武汉):《EDA技术基础与实践(Electronic Design Automation)》课程教学资源(实验内容)实验十二 电梯控制实验.pdf

- 中国地质大学(武汉):《EDA技术基础与实践(Electronic Design Automation)》课程教学资源(实验内容)实验十三 步进电机控制实验.pdf

- 《EDA技术基础与实践(Electronic Design Automation)》课程教学资源(实验参考资料)FPGA基础知识(FPGA设计的指导性原则、FPGA设计的具体准则).pdf

- 《EDA技术基础与实践(Electronic Design Automation)》课程教学资源(实验参考资料)FPGA设计流程指南.pdf

- 西北工业大学:大学生创新中心内部培训教材《SOPC系统设计入门教程》教学资源(PDF电子书,主编:邵舒渊、卢选民,共六章).pdf

- 《EDA技术基础与实践(Electronic Design Automation)》课程教学资源(实验参考资料)DE2中文用户手册(DE2教学开发板).pdf

- 中国地质大学(武汉):《数字电子技术 Digital Electronic Technology》课程教学资源(教学大纲).pdf

- 中国地质大学(武汉):《数字逻辑实验》课程教学资源(实验内容)实验一 门电路逻辑功能及测试(验证性).pdf

- 中国地质大学(武汉):《数字逻辑实验》课程教学资源(实验内容)实验二 组合逻辑电路(综合性).pdf

- 中国地质大学(武汉):《数字逻辑实验》课程教学资源(实验内容)实验三 触发器(验证性).pdf

- 中国地质大学(武汉):《数字逻辑实验》课程教学资源(实验内容)实验四 集成电路测试及研究(设计性).pdf

- 中国地质大学(武汉):《数字逻辑实验》课程教学资源(实验内容)实验五 集成计数器及寄存器(综合性).pdf

- 中国地质大学(武汉):《数字逻辑实验》课程教学资源(实验内容)实验六 译码器和数据选择器(综合性).pdf

- 中国地质大学(武汉):《数字逻辑实验》课程教学资源(实验内容)实验七 波形产生及单稳态触发器(设计性).pdf

- 中国地质大学(武汉):《数字逻辑实验》课程教学资源(实验内容)实验八 555时基电路(设计性).pdf

- 中国地质大学(武汉):《数字逻辑实验》课程教学资源(实验内容)实验九 竞争冒险(设计性).pdf

- 中国地质大学(武汉):《数字逻辑实验》课程教学资源(实验内容)实验十 数字定时器(设计性).pdf

- 中国地质大学(武汉):《数字逻辑实验》课程教学资源(实验内容)实验十一 四路优先判决电路(设计性).pdf

- 《现代通信原理 Modern Communication Principle》课程教学资源(课件讲稿)第1章 绪论.pdf

- 《现代通信原理 Modern Communication Principle》课程教学资源(课件讲稿)第2章 信道与噪声.pdf