兰州交通大学:《电子电路实践》课程教学资源(授课课件)EDA技术实验2:FPGA/CPLD结构与应用

EDA方法(设计)及实验 国家级电工电子实验教学示范中心

EDA方法(设计)及实验 国家级电工电子实验教学示范中心

第2章 FPGA/CPLD结构与应用 ⑩ 菌州克通大粤

第2章 FPGA/CPLD结构与应用

2.1 FPGA/CPLD的定义 FPGA-Field Programmable Gate Array CPLD-Complex Programmable Logic Device 菌州克通大粤

FPGA - Field Programmable Gate Array CPLD - Complex Programmable Logic Device 2.1 FPGA/CPLD的定义

2.2可编程逻辑器件的分类 1:按集成密度分:低密度(700门/片) 可编程逻辑器件(PLD) 简单PLD 复杂PLD PROM PLA PAL GAL CPLD FPGA ⑩ 菌州支通大学

2.2 可编程逻辑器件的分类 可编程逻辑器件(PLD) 简单 PLD 复杂 PLD PROM PLA PAL GAL CPLD FPGA 1:按集成密度分:低密度 (700门/片)

可编程逻辑器件的分类 2:按可编程逻辑器件的编程方式分: 一次性编程OTP器件 多次编程MTP器件 EPROM、E2PROM、 快闪存储器件的 优点是系统断电后编程信息不丢失,其中 EEPROM、快闪存储器件可编程100次, 只读存储器还设有保密位可以防止非法炮制 菌州克通大学

可编程逻辑器件的分类 2:按可编程逻辑器件的编程方式分: 一次性编程OTP器件 多次编程MTP器件 EPROM 、 、 快闪存储器件的 优点是系统断电后编程信息不丢失 ,其中 EEPROM、快闪存储器件可编程100次, 只读存储器还设有保密位可以防止非法炮制 E PROM 2

可编程逻辑器件的分类 3:按结构分:阵列型和门阵列型 阵列型PLD的基本结构由与阵列和或阵列组成。 简单PLD、EPLD、CPLD均属此类。(其中EPLD、 CPLD是从PAL、GAL发展起来的阵列型高密度PLD 器件,多数粟OM 和快闪存储器等编程技术 ,具有高密、高速、低耗等特点 现场可编程门阵列的结构由许多可编程单元(或 逻辑功能块)排成阵列组成。FPGA属此类。它类 似于掩膜可编程门阵列(MPGA),用户可通过编程将 这些模块连接起来实现不同的设计,它兼容了( MPGA),PLD的优点具有集成度高、更强的逻辑实现 能力、更好的设计灵活性。 菌州克通大粤

可编程逻辑器件的分类 3:按结构分:阵列型和门阵列型 阵列型PLD的基本结构由与阵列 和或阵列组成。 简单PLD、EPLD、CPLD均属此类。(其中EPLD、 CPLD是 从PAL、GAL发展起来的阵列型高密度PLD 器件,多数采用 和快闪存储器等编程技术 ,具有高密、高速、低耗等特点 现场可编程门阵列的结构由许多可编程单元(或 逻辑功能块 ) 排成阵列组成 。FPGA属此类 。它类 似于掩膜可编程门阵列(MPGA),用户可通过编程将 这些模块连接起来实现不同的设计,它兼容了( MPGA), PLD的优点具有集成度高、更强的逻辑实现 能力、更好的设计灵活性。 E PROM 2

2.3在系统可编程(ISP)技术 指对器件、电路板、整个电子系统的逻辑功能可随时进 行修改或重构的能力。是一种先进的编程方式。不需要 编程器,只需要通过计算机接口和编程电缆直接在对目 标系统编程。 支持SP技术的可编程逻辑器件成为在系统可编程器件 。采用ISP技术,使系统内硬件的功能就可以向软件一 样,通过编程很方便的被配置、重构、和升级。 多芯片SP编程方式,成为菊花链结构,各片共用一套 ISP编程接口,每片的SD输入端与前一片的SDO输出 端相连,最前面一片的SD端和最后一片的SDO端与 1SP编程口相连,构成链型结构。它只许5根线0 菌州克通大学

2.3 在系统可编程(ISP)技术 • 指对器件、电路板、整个电子系统的逻辑功能可随时进 行修改或重构的能力。是一种先进的编程方式。不需要 编程器,只需要通过计算机接口和编程电缆直接在对目 标系统编程。 • 支持ISP技术的可编程逻辑器件成为在系统可编程器件 。采用ISP技术,使系统内硬件的功能就可以向软件一 样,通过编程很方便的被配置、重构、和升级。 • 多芯片ISP编程方式,成为菊花链结构,各片共用一套 ISP编程接口,每片的SDI输入端与前一片的SDO输出 端相连,最前面一片的SDI端和最后一片的SDO端 与 ISP编程口相连,构成链型结构。它只许5根线()

2.4边界扫描技术JTAG (国际测试组织IEEE标准 ) 边界扫描测试是针对期间密度及/O接口数量 的增加,信号注入和测取难度越来越大而提出 的一种新的测试技术,他必须它不需要使用外 部物理测试探针来获得功能数据,JTAG技术 在器件正常工作时,器件的边界扫描单元能够 追踪引脚信号或是从器件逻辑信号中捕捉数据 ,在串行移出,与预期结果比较。通过JTAG测 试端口实现对SP器件的在系统编程,很容易 完成电路测试。它只需4根线(TDI测试数据入 、TDO出、TMS测试模式选择、TCK测试时钟 输入) 菌州克通大粤

2.4 边界扫描技术JTAG (国际测试组织IEEE标准) • 边界扫描测试是针对期间密度及I/O 接口数量 的增加,信号注入和测取难度越来越大而提出 的一种新的测试技术,他必须它不需要使用外 部物理测试探针来获得功能数据, JTAG技术 在器件正常工作时,器件的边界扫描单元能够 追踪引脚信号或是从器件逻辑信号中捕捉数据 ,在串行移出,与预期结果比较。通过JTAG测 试端口实现对ISP器件的在系统编程,很容易 完成电路测试。它只需4根线(TDI测试数据入 、TDO出、TMS测试模式选择、TCK测试时钟 输入)

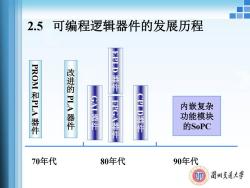

2.5可编程逻辑器件的发展历程 RPLD器 PROM村PL/器件 改进的/器件 器件 CPLD器件 内嵌复杂 功能模块 的SoPC 70年代 80年代 90年代 南葡州发通大粤

2.5 可编程逻辑器件的发展历程 70年代 80年代 90年代 PROM 和PLA 器 件 改 进 的PLA 器 件 GAL 器 件 FPGA 器 件EPLD 器 件 CPLD 器 件 内嵌复杂 功能模块 的SoPC

2.6EDA技术实现目标 1.超大规模可编程逻辑器件 2.半定制或全定制ASIC 3.混合ASIC ⑩ 菌州克通大婆

1. 超大规模可编程逻辑器件 2. 半定制或全定制ASIC 3. 混合ASIC 2.6 EDA技术实现目标 1. 超大规模可编程逻辑器件 2. 半定制或全定制ASIC 3. 混合ASIC

按次数下载不扣除下载券;

注册用户24小时内重复下载只扣除一次;

顺序:VIP每日次数-->可用次数-->下载券;

- 兰州交通大学:《电子电路实践》课程教学资源(授课课件)电子工艺实习3:PCB设计与制作.pdf

- 兰州交通大学:《电子电路实践》课程教学资源(授课课件)EDA技术实验1:课程概述.pdf

- 兰州交通大学:《电子电路实践》课程教学资源(授课课件)电子工艺实习2:收音机的组装与调试.pdf

- 兰州交通大学:《电子电路实践》课程教学资源(授课课件)电子工艺实习1:数字万用表的组装与调试.pdf

- 兰州交通大学:《电子电路实践》课程教学资源(授课课件)数电实验7:555定时器.pdf

- 兰州交通大学:《电子电路实践》课程教学资源(授课课件)数电实验6:计数器.pdf

- 兰州交通大学:《电子电路实践》课程教学资源(授课课件)数电实验5:触发器.pdf

- 兰州交通大学:《电子电路实践》课程教学资源(授课课件)数电实验4:优先编码器的设计(EWB).pdf

- 兰州交通大学:《电子电路实践》课程教学资源(授课课件)数电实验3:译码器和数据选择器.pdf

- 兰州交通大学:《电子电路实践》课程教学资源(授课课件)数电实验2:加法器的设计与应用.pdf

- 兰州交通大学:《电子电路实践》课程教学资源(授课课件)数电实验1:基本门电路逻辑功能测试.pdf

- 兰州交通大学:《电子电路实践》课程教学资源(授课课件)模电实验8:模拟低通滤波器频率特性测试.ppt

- 兰州交通大学:《电子电路实践》课程教学资源(授课课件)数电实验:课程介绍.pdf

- 兰州交通大学:《电子电路实践》课程教学资源(授课课件)模电实验7:RC桥式振荡电路实验.pdf

- 兰州交通大学:《电子电路实践》课程教学资源(授课课件)模电实验6:低频OTL功率放大电路实验.pdf

- 兰州交通大学:《电子电路实践》课程教学资源(授课课件)模电实验5:集成运放的设计与应用.pdf

- 兰州交通大学:《电子电路实践》课程教学资源(授课课件)模电实验4:差分放大电路实验.pdf

- 兰州交通大学:《电子电路实践》课程教学资源(授课课件)模电实验3:负反馈放大电路实验.pdf

- 兰州交通大学:《电子电路实践》课程教学资源(授课课件)模电实验2:晶体管单管共射放大电路实验.pdf

- 兰州交通大学:《电子电路实践》课程教学资源(授课课件)模电实验1:常用仪器仪表的使用练习.pdf

- 兰州交通大学:《电子电路实践》课程教学资源(授课课件)EDA技术实验3:EDA开发.pdf

- 兰州交通大学:《电子电路实践》课程教学资源(授课课件)EDA技术实验4:Verilog语言.pdf

- 西安电子科技大学:LTCC材料在T/R组件中的应用与发展趋势(主讲:徐自强).pdf

- 西安电子科技大学:《毫米波雷达综合实验》课程教学资源(课件讲稿)第1讲 雷达原理及其应用简介(主讲:杨明磊).pdf

- 西安电子科技大学:《毫米波雷达综合实验》课程教学资源(课件讲稿)第2讲 毫米波雷达综合实验平台介绍.pdf

- 西安电子科技大学:《毫米波雷达综合实验》课程教学资源(课件讲稿)第3讲 毫米波雷达测距原理及实验.pdf

- 西安电子科技大学:《毫米波雷达综合实验》课程教学资源(课件讲稿)第4讲 毫米波雷达测速原理及实验.pdf

- 西安电子科技大学:《毫米波雷达综合实验》课程教学资源(课件讲稿)第5讲 毫米波雷达测角原理及实验.pdf

- 西安电子科技大学:《毫米波雷达综合实验》课程教学资源(课件讲稿)第6讲 毫米波雷达检测、跟踪原理及实验.pdf

- 西安电子科技大学:《毫米波雷达综合实验》课程教学资源(课件讲稿)第7讲 生命体征检测实验.pdf

- 西安电子科技大学:《移动通信系统》课程教学课件(讲稿)第一讲 无线通信概述(主讲:高洋).pdf

- 西安电子科技大学:《移动通信系统》课程教学课件(讲稿)第二讲 移动通信信道.pdf

- 西安电子科技大学:《移动通信系统》课程教学课件(讲稿)第三讲 无线信源与信道编码.pdf

- 西安电子科技大学:《移动通信系统》课程教学课件(讲稿)第四讲 无线调制技术.pdf

- 西安电子科技大学:《移动通信系统》课程教学课件(讲稿)第五讲 无线分集技术.pdf

- 西安电子科技大学:《移动通信系统》课程教学课件(讲稿)第六讲 无线抗干扰和抗衰落技术.pdf

- 西安电子科技大学:《移动通信系统》课程教学课件(讲稿)第七讲 蜂窝移动多址接入技术.pdf

- 西安电子科技大学:《移动通信系统》课程教学课件(讲稿)第八讲 2G蜂窝移动通信系统.pdf

- 西安电子科技大学:《移动通信系统》课程教学课件(讲稿)第九讲 3G蜂窝移动通信系统概述.pdf

- 西安电子科技大学:《移动通信系统》课程教学课件(讲稿)第十讲 WCDMA移动通信系统.pdf