烟台理工学院:《数字电路与逻辑设计》课程教学资源(课件讲稿)第四章 组合逻辑电路 4.5 奇偶检验器和数值比较器

数字电子技术 第四章组合} 4.5奇偶检验器和数值比较器 4.5.1奇偶检验器 在实际电路中,码元的变化不可能绝对同 时发生,当两位或两位以上的码元转态发生变 化时,很有可能出现瞬态代码。如当 0001→0010时,实际可能是0001→0011→0010 故在数字电路中,要求代码按一定顺序变 化时,常采用可靠性编码。如格雷码、奇偶校 验码。 1.格雷码

第四章 组合逻辑电路 4.5 奇偶检验器和数值比较器 4.5.1 奇偶检验器 在实际电路中,码元的变化不可能绝对同 时发生,当两位或两位以上的码元转态发生变 化时,很有可能出现瞬态代码。如当 0001→0010时,实际可能是0001→0011→0010. 故在数字电路中,要求代码按一定顺序变 化时,常采用可靠性编码。如格雷码、奇偶校 验码。 1.格雷码

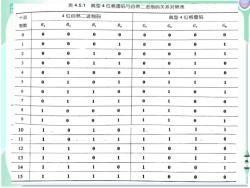

表4.5.1 典型4位格雷码与自然二进制码关系对照表 十进 4位自然二进制码 典型4位格雷码 制数 B, B, B, B G G G G 0 0 0 0 0 0 0 0 0 1 0 0 0 1 0 0 0 1 2 0 0 1 0 0 0 1 1 0 0 1 1 0 0 1 0 0 1 0 0 0 1 1 0 5 0 1 0 1 0 1 1 6 0 1 1 0 0 1 1 7 0 1 1 1 0 1 0 0 8 1 0 0 0 1 1 0 0 9 1 0 0 1 1 1 0 1 10 1 0 1 0 1. 1 1 1 11 1 0-.. 1 1 1 1 1 0 12 1 1 0 0 1 0 1 0 13 1 1 0 1 1 0 1 1 14 1 1 1 0 1 0 0 1 15 1 1 1 1 1 0 0 0

第四章 组合逻辑电路

数字电子技术 第四章 组合 其特点:任意两个相邻代码之间只有一位 码元不同,且0和最大数(21)对应的格雷码 之间也只有一位不同,即首尾相连。它是一种 循环码。 典型格雷码与自然二进制码转换规律: G=B,①B+1 即G=B⊕B,G1=B1⊕B2 G2=B2⊕B3,G3=B3⊕0=B3

第四章 组合逻辑电路 其特点:任意两个相邻代码之间只有一位 码元不同,且0和最大数(2 n-1)对应的格雷码 之间也只有一位不同,即首尾相连。它是一种 循环码。 典型格雷码与自然二进制码转换规律: Gi Bi Bi1 2 2 3 3 3 3 0 0 1 1 1 2 G B B G B 0 B G B B G B B , 即

数字电子技术 第四章组合} 2.奇偶校验码 二进制信息在传输过程中也可能出现错误, 为了便于发现和校正错误,常采用奇偶校验码。 奇偶校验码=传送信息位+1位奇偶校验位。 若奇偶校验码中1的个数为奇数称为奇校验,1 的个数是偶数则称为偶校验。 需要注意,利用奇偶校验码只能发现奇数 个错误,但没有错误定位和纠错能力,发现错 误就只能重新传送信息。但其实现电路简单

第四章 组合逻辑电路 2.奇偶校验码 二进制信息在传输过程中也可能出现错误, 为了便于发现和校正错误,常采用奇偶校验码。 奇偶校验码=传送信息位+1位奇偶校验位。 若奇偶校验码中1的个数为奇数称为奇校验,1 的个数是偶数则称为偶校验。 需要注意,利用奇偶校验码只能发现奇数 个错误,但没有错误定位和纠错能力,发现错 误就只能重新传送信息。但其实现电路简单

数字电子技术 第四章 组合} 二、奇偶校验电路—异或门 n个变量的异或运算,输入组合中1的个数 为奇数,则运算结果为1;否则,运算结果为0。 YoD P.P 奇输出 (a) (b)速度更快 Ps YoD 奇输出 (b) 图4.5.19位奇偶检脸电路 (a)串联型(b)树型

第四章 组合逻辑电路 二、奇偶校验电路——异或门 n个变量的异或运算,输入组合中1的个数 为奇数,则运算结果为1;否则,运算结果为0。 (b)速度更快

数字电子技术 第四章组合逻辑电路 P P P2 P2 常用的9位奇 Yop YoD 偶校验器集成 电路是74180 P9 P9 和74280(均 为树形结构) P P2 福 P3 P YoD P 位 Yop Yoo 9 P9 奇输出 Py P P2 P2 P3 Yop -YoD Yop (b)的速度 奇输出 更快 (a) (b) 图4.5.2多位奇偶检验电路 (a)25位奇数检验(b)81位奇数检验

第四章 组合逻辑电路

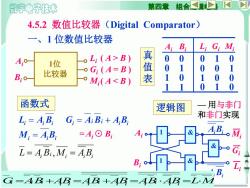

数字电子技术 第四章组合 4.5.2数值比较器 (Digital Comparator) 一、1位数值比较器 A; B Li G:Mi 0 0 0 1位 0 Li(A>B) Gi(A=B) 值 1 0 0 B 比较器 0 M(A<B) 表 0 0 函数式 逻辑图 用与非门 L=AB G:=Ai Bi+AB 和非门实现 M:=AB =A:⊙B: Ai & L=ABi,M=AB B =AB+4B=4B+4B-4B.4B-L.M

第四章 组合逻辑电路 4.5.2 数值比较器(Digital Comparator) 一、1 位数值比较器 0 0 0 1 1 0 1 1 0 1 0 0 0 1 1 0 0 0 1 0 真 值 表 函数式 逻辑图 — 用与非门 和非门实现 Ai Bi Li Gi Mi Li ( A > B ) Gi ( A = B ) Mi ( A < B ) = Ai ⊙ Bi 1位 比较器 Ai Bi Ai & 1 & B 1 & i Mi Gi Li i i i i L Ai B ,M A B Gi AiBiAiBi AiBiAiBi AiBi AiBi LM

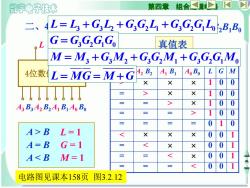

数字电子技术 第四章 组合} 二、4L=L3+G3L2+GG2L1+G,G,G1Lo2B,B L G=G3G2GGo 真值表 M=M3+G3M2+G3G2M+G3G2GMo 4位数 L=MG-M+G A2 B2 A B Ao Bo × × × 三 × > A3 B3A2 B2A1B1A0 Bo A>B L=1 X A=B G=1 × A<B M=1 < 0 电路图见课本158页 图3.2.12

第四章 组合逻辑电路 二、4 位数值比较器 A = A3A2A1A0 A > B L = 1 A = B A 1 0 0 = > 1 0 0 = = > 1 0 0 = = = > 1 0 0 = = = = 0 1 0 < 0 0 1 = < 0 0 1 = = < 0 0 1 = = = < 0 0 1 B = B3B2B1B0 L G M 4位数值比较器 A3 B3A2 B2A1B1 A0B0 L L G L G G L G G G L 3 3 2 3 2 1 3 2 1 0 G G G G G 3 2 1 0 M M G M G G M G G G M 3 3 2 3 2 1 3 2 1 0 L MG M G 电路图见课本158页 图3.2.12

数字电子技述 第四章组合悬} 4位集成数值比较器的真值表 比较输入 级联输入 输出 A:B3 A2B2 A B AoBo AB FA × × × × 0 0 × × 0 0 0 0 × 0 0 0 0 0 0 0 0 0 0 0 0 < × × X × 0 0 × X × 0 0 < X × × X 1 0 0 < × × X 1 0 0 级联输入:供扩展使用,一般接低位芯片的比较输出

第四章 组合逻辑电路 比 较 输 入 级 联 输 入 输 出 A3B3 A2B2 A1B1 A0B0 AB FA B > 0 0 1 = > 0 0 1 = = > 0 0 1 = = = > 0 0 1 = = = = 0 0 1 0 0 1 = = = = 0 1 0 0 1 0 = = = = 1 0 0 1 0 0 < 1 0 0 = < 1 0 0 = = < 1 0 0 = = = < 1 0 0 4 位集成数值比较器的真值表 级联输入:供扩展使用,一般接低位芯片的比较输出

数字电子技术 第四章组合} Bo 集成数值比较器 74LS85(TTL) 161514131211109 748574LS85 扩展:两片4位数值比较器 1234 5678 → 8位数值比较器 B3AKBA=BA-BEB月BYAB地 B3 A3 B2 A2 B1A1 AB 低位比较结果A>B H9- 高位比较结果 FAB FA-E FA-B FA<B A=B 比较输出

第四章 组合逻辑电路 扩展: 级 联 输 入 集成数值比较器 74LS85 (TTL) 两片 4 位数值比较器 74LS85 AB 74LS85 AB VCC A3 B2 A2 A1 B1 A0 B0 B3 AB FA>B FA=B FAB FAB B7 A7 B6 A6 B5 A5 B4 A4 B3 A3 B2 A2 B1 A1 B0 A0 比较输出

按次数下载不扣除下载券;

注册用户24小时内重复下载只扣除一次;

顺序:VIP每日次数-->可用次数-->下载券;

- 烟台理工学院:《数字电路与逻辑设计》课程教学资源(课件讲稿)第四章 组合逻辑电路 4.3 编码器和译码器.pdf

- 烟台理工学院:《数字电路与逻辑设计》课程教学资源(课件讲稿)第四章 组合逻辑电路 4.4 数据选择器和分配器.pdf

- 烟台理工学院:《数字电路与逻辑设计》课程教学资源(课件讲稿)第四章 组合逻辑电路 4.2 加法器.pdf

- 烟台理工学院:《数字电路与逻辑设计》课程教学资源(课件讲稿)第四章 组合逻辑电路 4.1 组合电路的基本分析方法和设计方法.pdf

- 烟台理工学院:《数字电路与逻辑设计》课程教学资源(课件讲稿)第四章 组合逻辑电路 4.0 概述.pdf

- 烟台理工学院:《数字电路与逻辑设计》课程教学资源(课件讲稿)第二章 门电路(小结).pdf

- 烟台理工学院:《数字电路与逻辑设计》课程教学资源(课件讲稿)第二章 门电路 2.5 TTL集成门电路.pdf

- 烟台理工学院:《数字电路与逻辑设计》课程教学资源(课件讲稿)第二章 门电路 2.4 CMOS反相器.pdf

- 烟台理工学院:《数字电路与逻辑设计》课程教学资源(课件讲稿)第二章 门电路 2.3 分立元器件门电路.pdf

- 烟台理工学院:《数字电路与逻辑设计》课程教学资源(课件讲稿)第二章 门电路 2.2 半导体二极管、三极管和MOS管的开关特性.pdf

- 烟台理工学院:《数字电路与逻辑设计》课程教学资源(课件讲稿)第二章 门电路 2.1 概述.pdf

- 烟台理工学院:《数字电路与逻辑设计》课程教学资源(课件讲稿)第一章 逻辑代数与EDA技术的基础知识(思维导图).pdf

- 烟台理工学院:《数字电路与逻辑设计》课程教学资源(课件讲稿)第一章 逻辑代数与EDA技术的基础知识(小结).pdf

- 烟台理工学院:《数字电路与逻辑设计》课程教学资源(课件讲稿)第一章 逻辑代数与EDA技术的基础知识(4/4)1.3 逻辑函数的表示方法及其相互之间的转换.pdf

- 烟台理工学院:《数字电路与逻辑设计》课程教学资源(课件讲稿)第一章 逻辑代数与EDA技术的基础知识(3/4)1. 2 逻辑函数的化简方法.pdf

- 烟台理工学院:《数字电路与逻辑设计》课程教学资源(课件讲稿)第一章 逻辑代数与EDA技术的基础知识(2/4)1.1 基本概念、公式和定理.pdf

- 烟台理工学院:《数字电路与逻辑设计》课程教学资源(课件讲稿)第一章 逻辑代数与EDA技术的基础知识(1/4)1.0 概述.pdf

- 合肥工业大学:《数字电子技术基础》课程教学资源(课件讲稿)第七章 半导体存储器.pdf

- 合肥工业大学:《数字电子技术基础》课程教学资源(课件讲稿)第六章 时序逻辑电路.pdf

- 合肥工业大学:《数字电子技术基础》课程教学资源(课件讲稿)第五章 触发器.pdf

- 烟台理工学院:《数字电路与逻辑设计》课程教学资源(课件讲稿)第四章 组合逻辑电路 4.6 用MSI实现组合逻辑函数.pdf

- 烟台理工学院:《数字电路与逻辑设计》课程教学资源(课件讲稿)第四章 组合逻辑电路 4.7 只读存储器(ROM).pdf

- 烟台理工学院:《数字电路与逻辑设计》课程教学资源(课件讲稿)第四章 组合逻辑电路 4.8 组合电路中的竞争冒险.pdf

- 烟台理工学院:《数字电路与逻辑设计》课程教学资源(课件讲稿)第五章 触发器 5.0 概述.ppt

- 烟台理工学院:《数字电路与逻辑设计》课程教学资源(课件讲稿)第四章 组合逻辑电路(小结).pdf

- 烟台理工学院:《数字电路与逻辑设计》课程教学资源(课件讲稿)第五章 触发器 5.1 基本触发器.ppt

- 烟台理工学院:《数字电路与逻辑设计》课程教学资源(课件讲稿)第五章 触发器 5.2 同步触发器.ppt

- 烟台理工学院:《数字电路与逻辑设计》课程教学资源(课件讲稿)第五章 触发器 5.3 边沿触发器.ppt

- 烟台理工学院:《数字电路与逻辑设计》课程教学资源(课件讲稿)第五章 触发器 5.4 触发器的电气特性.ppt

- 烟台理工学院:《数字电路与逻辑设计》课程教学资源(课件讲稿)第五章 触发器(小结).ppt

- 烟台理工学院:《数字电路与逻辑设计》课程教学资源(课件讲稿)第六章 时序逻辑电路 6.0 概述.ppt

- 烟台理工学院:《数字电路与逻辑设计》课程教学资源(课件讲稿)第六章 时序逻辑电路 6.1 时序电路的基本分析和设计方法.ppt

- 烟台理工学院:《数字电路与逻辑设计》课程教学资源(课件讲稿)第六章 时序逻辑电路 6.2 计数器(Counter).ppt

- 烟台理工学院:《数字电路与逻辑设计》课程教学资源(课件讲稿)第六章 时序逻辑电路 6.3 寄存器和读/写存储器(Register and Random Access Memory).ppt

- 烟台理工学院:《数字电路与逻辑设计》课程教学资源(课件讲稿)第六章 时序逻辑电路 6.4 顺序脉冲发生器.ppt

- 烟台理工学院:《数字电路与逻辑设计》课程教学资源(课件讲稿)第六章 时序逻辑电路(小结).ppt

- 烟台理工学院:《数字电路与逻辑设计》课程教学资源(课件讲稿)第六章 时序逻辑电路 6.5 可编程逻辑器件(Programmable Logic Device,PLD).ppt

- 烟台理工学院:《数字电路与逻辑设计》课程教学资源(课件讲稿)第七章 555定时器脉冲产生与整形电路 7.0 概述 7.1 555定时器.ppt

- 烟台理工学院:《数字电路与逻辑设计》课程教学资源(课件讲稿)第七章 555定时器脉冲产生与整形电路 7.2 施密特触发器(Schmitt Trigger).ppt

- 烟台理工学院:《数字电路与逻辑设计》课程教学资源(课件讲稿)第七章 555定时器脉冲产生与整形电路7.3 单稳态触发器.ppt