宁夏师范学院:《数字电路》课程电子教案(PPT教学课件)第四章 组合逻辑电路(2/4)

第4章组合逻辑电路

第4章 组合逻辑电路

常用组合逻辑电路种类很多,主要有全加器、 译码器、编码器、 多路选择器、多路分配器、数 值比较器、奇偶检验电路等。 常用组合电路均有中规模集成电路 (MSI) 产品。 MS组合部件具有功能强、兼容性好、体积小、功 耗低、使用灵活等优点,因此得到广泛应用。本节主要 介绍几种典型MS组合逻辑部件的功能及应用

常用组合逻辑电路种类很多,主要有全加器、 译码器、编码器、多路选择器、多路分配器、数 值比较器、奇偶检验电路等。 常用组合电路均有中规模集成电路(MSI) 产品。 MSI组合部件具有功能强、兼容性好、体积小、功 耗低、使用灵活等优点,因此得到广泛应用。本节主要 介绍几种典型MSI组合逻辑部件的功能及应用

第三节 加法器 两个二进制数之间的算术运算无论是加、减、乘、 除,在计算机中都是化做若干步加法运算进行的。因此, 加法器是构成算术运算器的基本单元。 一、1位如法器 1、半加器 不考虑低位来的进位加法叫半加。 半加器:能完成半加功能的电路叫半加器

半加器:能完成半加功能的电路叫半加器。 不考虑低位来的进位加法叫半加。 两个二进制数之间的算术运算无论是加、减、乘、 除,在计算机中都是化做若干步加法运算进行的。因此, 加法器是构成算术运算器的基本单元

1、半加器 能对两个1位二进制数进行相加而求得和及进位的逻辑 电路称灯半加器。 半加器真值表 本位 B Q S B S 的和 0 0 0 & 数加 向高 0 1 1 0 位的 1 0 1 0 进位 半加器电路图 0 M S,=AB,+AB,=A⊕B B;o C=AB 半加器符号

1、半加器 能对两个1位二进制数进行相加而求得和及进位的逻辑 电路称为半加器。 半加器真值表 Ai Bi Si Ci 0 0 0 1 1 0 1 1 0 0 1 0 1 0 0 1 i i i i i i i i i i C A B S A B A B A B = = + = =1 & Ai Bi Si Ci Ai Bi Si Ci ∑ CO 半加器符号 半加器电路图 数加 本位 的和 向高 位的 进位

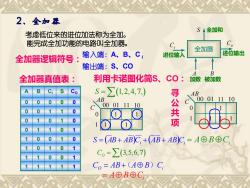

2、全加器 S4全加和 考虑低位来的进位加法称为全加。 能完成全加功能的电路叫全加器。 C C。 全加器 全加器逻辑符号: 输入端:A、B、C; 进位输入 进位输出 输出端:S、CO B 全加器真值表: 利用卡诺图化简S、C0:加数被加数 B =∑(1,2,4,7,) 寻 、A AB 0011110 C 00011110 0 0 0 1 共项 S=AB+ABC+AB+AB)C=A B C Co=∑(3,5,6,7) CO=AB+(A⊕B)C =A⊕B⊕C

AB C 00 01 11 10 0 1 1 1 1 1 AB C 00 01 11 10 0 1 1 1 1 1 考虑低位来的进位加法称为全加。 能完成全加功能的电路叫全加器。 全加器逻辑符号:输入端:A、B、C i 输出端:S、CO 全加器真值表: A B CI S CO 0 0 0 0 0 0 0 1 1 0 0 1 0 1 0 0 1 1 0 1 1 0 0 1 0 1 0 1 0 1 1 1 0 0 1 1 1 1 1 1 利用卡诺图化简S、CO: S =(1,2,4,7,) ( ) ( ) S = AB+ AB Ci + AB+ AB Ci = A BCi CO =(3,5,6,7) CO = AB+(A B)Ci 寻 公 共 项 = A B Ci 进位输入 Ci 加数 A 全加和 全加器 进位输出 被加数 S Co B

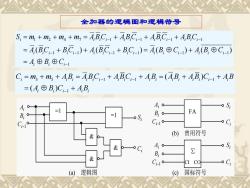

全加器的逻辑图和逻辑符号 S =m+m2 +ma+m=4B.C+4B.C+4B.C+4B.C =A(B,C-1+B,C-)+A(BC,1+B,C-)=A(B,田C-)+A(B®C,-) =A4田B®C- C=ms +ms +AB=ABC+ABC+AB =(AB +AB)C+4B =(A©B)C,-1+A,B Aio Bio FA C Ci° (b) 曾用符号 Bi C-1o- CI co a) 逻辑图 (c) 国标符号

i i i i i i i i i i i i i i i i i i i i i i A B C AB C m m AB ABC ABC AB AB AB C AB = + = + + = + + = + + − − − − 1 3 5 1 1 1 ( ) ( ) 全加器的逻辑图和逻辑符号 = 1 & & Ai Bi Ci-1 Si Ci (a) 逻辑图 (c) 国标符号 Ai Bi Ci-1 Si Ci Ai Bi Ci-1 Si Ci (b) 曾用符号 CI CO ∑ & = 1 F A 1 1 1 1 1 1 1 1 2 4 7 1 1 1 1 ( ) ( ) ( ) ( ) − − − − − − − − − − − = = + + + = + = + + + = + + + i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i i A B C A BC BC A BC BC A B C A B C S m m m m A BC A BC A BC A BC

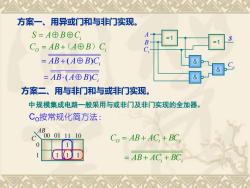

方案一、用异或门和与非门实现。 S=A⊕B⊕C CO=AB+(A⊕B)C =AB+(A田B)C =AB·(A⊕B)C 方案二、用与非门和与或非门实现。 中规模集成电路一般采用与或非门及非门实现的全加器。 Co按常规化简方法: AB 00011110 C Co=AB+AC+BC 0 =AB+AC BC

AB C 00 01 11 10 0 1 1 1 1 1 方案一、用异或门和与非门实现。 S = A BCi CO = AB+(A B)Ci ( ) = AB + A B Ci ( ) AB A B Ci = 方案二、用与非门和与或非门实现。 CO = AB+ ACi + BCi = AB + ACi + BCi 中规模集成电路一般采用与或非门及非门实现的全加器。 CO按常规化简方法: A & & B Ci Co s =1 =1 &

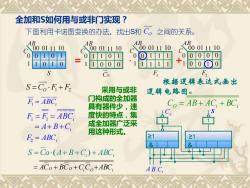

全加和S如何用与或非门实现? 下面利用卡诺图变换的办法,找出S和C。之间的关系。 A80011110 AB AB C00011110 AB 、00 011110 C00011110 00101 01101 0 11 00000 1 1010 11000 1 1 +ioo①0 S Co S=Co·F+F 根据逻辑表达式画出 采用与或非 逻辑电路图。 F=ABC 门构成的全加器 具有器件少,速 Co=AB+AC +BC F=F=ABC 度快的特点,集 =4+B+C 成全加器广泛采 用这种形式。 F=ABC S=Co.(A+B+C)+ABC ACo+BCo+CCo+ABC

AB C 00 01 11 10 0 1 F2 0 0 1 0 0 0 0 0 AB C 00 01 11 10 0 1 F1 1 1 1 0 1 1 1 1 全加和S如何用与或非门实现? 下面利用卡诺图变换的办法,找出S和 CO 之间的关系。 = · + S CO F1 + F2 = F1 = ABCi F1 = F1 = ABCi = A+ B +Ci F2 = ABCi ( ) S Co A+ B+Ci + ABCi = = ACO + BCO +Ci CO +ABCi 根据逻辑表达式画出 采用与或非 逻辑电路图。 门构成的全加器 具有器件少,速 度快的特点,集 成全加器广泛采 用这种形式。 AB C 00 01 11 10 0 1 S 1 1 1 0 1 0 0 0 AB C 00 01 11 10 0 1 C0 1 1 0 1 1 0 0 0 A B Ci Co s 1 1 CO = AB + ACi + BCi ≥1 & ≥1 &

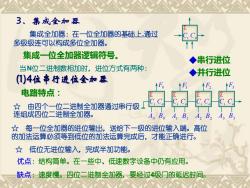

3、集成全加器 集成全加器:在一位全加器的基础上,通过 多级级连可以构成多位全加器。 集成一位全加器逻辑符号。 ◆串行进位 当N位二进制数相加时,进位方式有两种: ◆并行进位 (1)4位串行进位全加器 o ↑F F F 电路特点: ☆由四个一位二进制全加器通过串行级 连组成四位二进制全加器。 A。B。A1B1A2B A.B ☆每一位全加器的进位输出, 送给下一级的进位输入端。高位 的加法运算必须等到低位的加法运算完成后,才能正确进行。 ☆低位无进位输入,完成半加功能。 优点:结构简单。在一些中、低速数字设备中仍有应用。 缺点:速度慢。四位二进制全加器,要经过4级门的延迟时间

集成全加器:在一位全加器的基础上,通过 多级级连可以构成多位全加器。 集成一位全加器逻辑符号。 当N位二进制数相加时,进位方式有两种: ◆串行进位 ◆并行进位 ☆ 低位无进位输入,完成半加功能。 电路特点: ☆ 由四个一位二进制全加器通过串行级 连组成四位二进制全加器。 ☆ 每一位全加器的进位输出,送给下一级的进位输入端。高位 的加法运算必须等到低位的加法运算完成后,才能正确进行。 Σ Ci Co Σ Ci Co F0 A0 B0 Σ Ci Co F1 A1 B1 Σ Ci Co F2 A2 B2 Σ Ci Co F3 A3 B3 优点:结构简单。在一些中、低速数字设备中仍有应用。 缺点:速度慢。四位二进制全加器,要经过4级门的延迟时间

2)超前进位全加器。 (并行进位) 超前进位:是各级进位同时发生,高位加法不必等低位的运算结 果。所以工作速度得以提高。即:只用了一级门的传输延迟时间。 4位全加器的逻辑符号: 输入端:P加数,Q被加数。每组有四个输入。 C:进位输入端。 3 输出端:∑表示四位全加和输出端,C进位输 出端。 321 超前进位中规模集成电路型号有: 3210 54/74283,CC/CD4008

超前进位:是各级进位同时发生,高位加法不必等低位的运算结 果。所以工作速度得以提高。即:只用了一级门的传输延迟时间。 4位全加器的逻辑符号: 输入端:P 加数,Q 被加数。每组有四个输入。 C i 进位输入端。 输出端:∑表示四位全加和输出端,CO进位输 出端。 超前进位中规模集成电路型号有: 54/74283,CC/CD4008 (并行进位) 3 2 1 0 P Σ CO Q 3 2 1 0 3 2 1 0 Σ Ci

按次数下载不扣除下载券;

注册用户24小时内重复下载只扣除一次;

顺序:VIP每日次数-->可用次数-->下载券;

- 宁夏师范学院:《数字电路》课程电子教案(PPT教学课件)第四章 组合逻辑电路(4/4).ppt

- 宁夏师范学院:《数字电路》课程电子教案(PPT教学课件)第二章 逻辑代数基础(3/3).ppt

- 宁夏师范学院:《数字电路》课程电子教案(PPT教学课件)第五章 集成触发器(2/2).ppt

- 宁夏师范学院:《数字电路》课程电子教案(PPT教学课件)第五章 集成触发器(1/2).ppt

- 宁夏师范学院:《数字电路》课程电子教案(PPT教学课件)第四章 组合逻辑电路(1/4).ppt

- 宁夏师范学院:《数字电路》课程电子教案(PPT教学课件)第三章 集成逻辑门电路(2/2).ppt

- 宁夏师范学院:《数字电路》课程电子教案(PPT教学课件)第三章 集成逻辑门电路(1/2).ppt

- 宁夏师范学院:《数字电路》课程电子教案(PPT教学课件)第一章 绪论 Digital electric circuit.ppt

- 宁夏师范学院:《数字电路》课程电子教案(PPT教学课件)第二章 逻辑代数基础(2/3).ppt

- 宁夏师范学院:《数字电路》课程电子教案(PPT教学课件)第二章 逻辑代数基础(1/3).ppt

- 《数字电子技术》课程教学资源(课件讲稿)第3章 集成逻辑门.pdf

- 西安电子科技大学:《数字通信理论与系统》课程教学课件(研究生)第12章 多用户通信.pdf

- 西安电子科技大学:《数字通信理论与系统》课程教学课件(研究生)第11章 多信道协同传输技术.pdf

- 西安电子科技大学:《数字通信理论与系统》课程教学课件(研究生)第10章 信道均衡.pdf

- 西安电子科技大学:《数字通信理论与系统》课程教学课件(研究生)第9章 扩频通信概述.pdf

- 西安电子科技大学:《数字通信理论与系统》课程教学课件(研究生)第8章 信道编码.pdf

- 西安电子科技大学:《数字通信理论与系统》课程教学课件(研究生)第7章 通信信道与无线链路.pdf

- 西安电子科技大学:《数字通信理论与系统》课程教学课件(研究生)第6章 载波跟踪与符号同步.pdf

- 西安电子科技大学:《数字通信理论与系统》课程教学课件(研究生)第5章 AWGN信道下的数字解调.pdf

- 西安电子科技大学:《数字通信理论与系统》课程教学课件(研究生)第4章 数字调制与基带传输技术.pdf

- 宁夏师范学院:《数字电路》课程电子教案(PPT教学课件)第七章 脉冲产生与整形电路.ppt

- 宁夏师范学院:《数字电路》课程电子教案(PPT教学课件)第四章 组合逻辑电路(3/4).ppt

- 宁夏师范学院:《数字电路》课程电子教案(PPT教学课件)第九章 半导体存储器.ppt

- 宁夏师范学院:《数字电路》课程电子教案(PPT教学课件)第十章 可编程逻辑电路(器件).ppt

- 宁夏师范学院:《数字电路》课程电子教案(PPT教学课件)第六章 时序逻辑电路(3/3)6.4 计数器 6.4.3 集成计数器.ppt

- 宁夏师范学院:《数字电路》课程电子教案(PPT教学课件)第六章 时序逻辑电路(2/3)6.4 计数器 6.4.1 异步计数器 6.4.2 同步计数器.ppt

- 宁夏师范学院:《数字电路》课程电子教案(PPT教学课件)第八章 数模和模数转换器.ppt

- 宁夏师范学院:《数字电路》课程电子教案(PPT教学课件)第六章 时序逻辑电路(1/3)6.1 概述 6.2 时序逻辑电路的分析 6.3 寄存器、移位寄存器.ppt

- 《通信原理》课程教学资源(文献资料)MATLAB在通信中的仿真应用.pdf

- 北京理工大学:《通信原理》课程教学资源(实验指导)SystemView通信原理仿真实验指导书(2013).pdf

- 《通信原理》课程教学资源(实验指导)实验一 数字基带信号.pdf

- 《通信原理》课程教学资源(实验指导)实验三 载波同步.pdf

- 《通信原理》课程教学资源(实验指导)实验二 数字调制与解调.pdf

- 《通信原理》课程教学资源(实验指导)实验五 时分复用2DPSK,2FSK通信系统.pdf

- 《通信原理》课程教学资源(实验指导)实验六 PCM编译码.pdf

- 《通信原理》课程教学资源(实验指导)实验四 时分复用数字基带通信系统.pdf

- 石河子大学:《通信原理》课程教学资源(大纲教案)通信原理教案2013-2014-2(任课教师:田敏).doc

- 石河子大学:《通信原理》课程教学资源(大纲教案)通信原理实验大纲 The principle of communication.doc

- 石河子大学:《通信原理》课程教学资源(实验指导)通信原理仿真实验指导-MATLAB版.pdf

- 《通信原理》课程教学资源(实验指导)通信原理实验指导书(硬件).pdf