广东海洋大学:《VHDL程序设计语言》课程教学资源(PPT课件)第5章 VHDL主要描述语句

第五章 VHDL主要描述语句

第五章 VHDL主要描述语句

主要内容 ·概述 ·行为描述语句 ·结构描述语句

主要内容 • 概 述 • 行为描述语句 • 结构描述语句

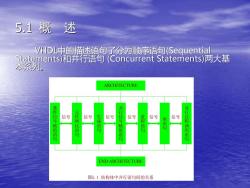

5.1概述 VHDL中的述语句了分为顺序语句(Sequential Statements)和并行语句(Concurrent Statements)两大基 本系列。 ARCHITECTURE 条 0 信号 信号 信号 生 信号 信号 信号赋值语句 成 灌信号 块 化语句 语 赋 并行过程调用语句 句 END ARCHITECTURE 图5.1结构体中并行语句间的关系

5.1 概 述 VHDL中的描述语句了分为顺序语句(Sequential Statements)和并行语句 (Concurrent Statements)两大基 本系列。 图5.1 结构体中并行语句间的关系 生 成 语 句 元 件 例 化 语 句 进 程 语 句 并 行 信 号 赋 值 语 句 并 行 过 程 调 用 语 句 块 语 句 条 件 信 号 赋 值 语 句 END ARCHITECTURE ARCHITECTURE 信号 信号 信号 信号 信号 信号

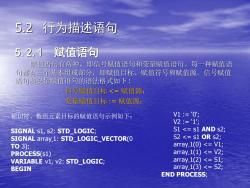

5.2行为描述语句 5.2.1赋值语句 赋值语句有两种,即信号赋值语句和变量赋值语句。每一种赋值语 句都有三个基本组成部分,即赋值目标、赋值符号和赋值源。信号赋值 语句和变量赋值语句的语法格式如下: 信号赋值目标<=赋值源: 变量赋值目标:三赋值源; 标识符、数组元素目标的赋值语句示例如下: V1:=0'g V2:=1'9 SIGNAL s1,s2:STD_LOGIC; S1 <s1 AND s2; SIGNAL array.1:STD_LOGIC_VECTOR(0 S2<=s10Rs2; T03): aray.1(0)<=V1; PROCESS(s1) aray.1(1)<=V2; VARIABLE v1,v2:STD_LOGIC; aray1(2)<=S1; BEGIN array..1(3)<=S2; END PROCESS;

5.2 行为描述语句 5.2.1 赋值语句 赋值语句有两种,即信号赋值语句和变量赋值语句。每一种赋值语 句都有三个基本组成部分,即赋值目标、赋值符号和赋值源。信号赋值 语句和变量赋值语句的语法格式如下 : 信号赋值目标 <= 赋值源; 变量赋值目标 := 赋值源; 标识符、数组元素目标的赋值语句示例如下: SIGNAL s1, s2: STD_LOGIC; SIGNAL array 1: STD_LOGIC_VECTOR(0 TO 3); PROCESS(s1) VARIABLE v1, v2: STD_LOGIC; BEGIN V1 := ‘0’; V2 := ‘1’; S1 <= s1 AND s2; S2 <= s1 OR s2; array 1(0) <= V1; array 1(1) <= V2; array 1(2) <= S1; array 1(3) <= S2; END PROCESS;

5.2.2并行信号赋值语句 1.一般信号赋值语句 信号赋值目标<=延迟选项表达式延迟表达式: 例5.1四位并行加法器的数据流描述。 LIBRARY IEEE; ARCHITECTURE ADD4 concumt OF ADD4 IS USE IEEE.STD LOGIC 1164.ALL; -定义包含有进位的SUM信号 USE IEEE.STD LOGIC UNSIGNED.ALL SIGNAL SUMINT:STD LOGIC_VECTOR( ENTITY ADD4 IS 4 DOWNTO 0); PORT( BEGIN A:IN STD LOGIC VECTOR(3 DOWNTO 0); SUMINT<=('0'&A)+(0'&B)+ B:IN STD_LOGIC_VECTOR(3 DOWNTO 0);("0000"&CIN)AFTER 10 ns; CIN IN STD LOGIC; COUT <SUMINT(4)AFTER 15 ns; SUM OUT STD LOGIC_VECTOR( SUM <SUMINT(3 DOWNTO 0)AFTER 3 DOWNTO 0); 15ns; COUT OUT STD LOGIC END ADD4_concurnt; END ADD4;

5.2.2 并行信号赋值语句 1.一般信号赋值语句 信号赋值目标 <= 延迟选项 表达式 延迟表达式; 例5.1 四位并行加法器的数据流描述。 LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL ENTITY ADD4 IS PORT ( A: IN STD_LOGIC_VECTOR (3 DOWNTO 0); B: IN STD_LOGIC_VECTOR (3 DOWNTO 0); CIN : IN STD_LOGIC; SUM : OUT STD_LOGIC_VECTOR ( 3 DOWNTO 0); COUT : OUT STD_LOGIC ); END ADD4; ARCHITECTURE ADD4_concurnt OF ADD4 IS -- 定义包含有进位的SUM信号 SIGNAL SUMINT: STD_LOGIC_VECTOR( 4 DOWNTO 0); BEGIN SUMINT <= ('0' & A) + ('0' & B) + ("0000" & CIN) AFTER 10 ns; COUT <= SUMINT(4) AFTER 15 ns; SUM <= SUMINT(3 DOWNTO 0) AFTER 15 ns; END ADD4_concurnt;

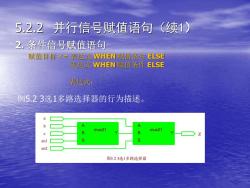

5.2.2并行信号赋值语句(续1) 2,条件信号赋值语句 赋值目标<兰表达式WHEN赋值条件ELSE 表达式WHEN赋值条件ELSE 表达式: 例5.23选1多路选择器的行为描述。 A B mux21 mux21 en2 图5.23选1多路选择器

5.2.2 并行信号赋值语句(续1) 2. 条件信号赋值语句 赋值目标 <= 表达式 WHEN 赋值条件 ELSE 表达式 WHEN 赋值条件 ELSE … 表达式; 例5.2 3选1多路选择器的行为描述。 S B A Y mux21 S B A Y mux21 a b c en2 en1 z 图5.2 3选1多路选择器

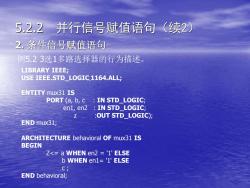

5.2.2 并行信号赋值语句(续2) 2.条件信号赋值语句 例5.23选1多路选择器的行为描述。 LIBRARY IEEE; USE IEEE.STD LOGIC1164.ALL; ENTITY mux31 IS PORT (a,b,c IN STD_LOGIC; en1,en2 IN STD LOGIC; OUT STD_LOGIC); END mux31; ARCHITECTURE behavioral OF mux31 IS BEGIN Z<=a WHEN en2 ='1'ELSE b WHEN en1='1'ELSE Ci END behavioral;

5.2.2 并行信号赋值语句(续2) 2. 条件信号赋值语句 例5.2 3选1多路选择器的行为描述。 LIBRARY IEEE; USE IEEE.STD_LOGIC 1164.ALL; ENTITY mux31 IS PORT (a, b, c : IN STD_LOGIC; en1, en2 : IN STD_LOGIC; z :OUT STD_LOGIC); END mux31; ARCHITECTURE behavioral OF mux31 IS BEGIN Z<= a WHEN en2 = '1' ELSE b WHEN en1= '1' ELSE c ; END behavioral;

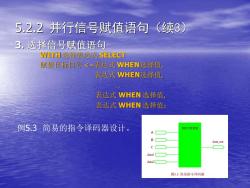

5.2.2并行信号赋值语句(续3) 3,选择信号赋值语句 WITH选择表达式SELECT 赋值目标信号<=表达式WHEN选择值, 表达式WHEN选择值, jj. 表达式WHEN选择值, 表达式WHEN选择值; 例5.3简易的指令译码器设计。 DECODER data out data2 图53简易指令译码器

5.2.2 并行信号赋值语句(续3) 3. 选择信号赋值语句 WITH 选择表达式 SELECT 赋值目标信号 <=表达式 WHEN选择值, 表达式 WHEN选择值, … 表达式 WHEN 选择值, 表达式 WHEN 选择值; 例5.3 简易的指令译码器设计。 B A 图5.3 简易指令译码器 data1 data2 data out C DECODER

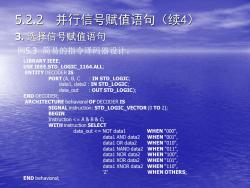

5.2.2 并行信号赋值语句(续4) 3,选择信号赋值语句 例5.3简易的指令译码器设计。 LIBRARY IEEE; USE IEEE.STD LOGIC 1164.ALL; ENTITY DECODER IS PORT(A,B,C:IN STD LOGIC; data1,data2:IN STD LOGIC; data out OUT STD_LOGIC); END DECODER: ARCHITECTURE behavioral OF DECODER IS SIGNAL instruction:STD_LOGIC_VECTOR(0 TO 2); BEGIN Instruction <=A B&C; WITH instruction SELECT data out <NOT data1 WHEN "00O" data1 AND data2 WHEN "001" data1 OR data2 WHEN "010" data1 NAND data2 WHEN "011" data1 NOR data2 WHEN "100" data1 XOR data2 WHEN "101" data1 XNOR data2 WHEN "110", WHEN OTHERS; END behavioral;

5.2.2 并行信号赋值语句(续4) 3. 选择信号赋值语句 例5.3 简易的指令译码器设计。 LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY DECODER IS PORT (A, B, C : IN STD_LOGIC; data1, data2 : IN STD_LOGIC; data_out : OUT STD_LOGIC); END DECODER; ARCHITECTURE behavioral OF DECODER IS SIGNAL instruction: STD_LOGIC_VECTOR (0 TO 2); BEGIN Instruction <= A & B & C; WITH instruction SELECT data_out <= NOT data1 WHEN "000", data1 AND data2 WHEN "001", data1 OR data2 WHEN "010", data1 NAND data2 WHEN "011", data1 NOR data2 WHEN "100", data1 XOR data2 WHEN "101", data1 XNOR data2 WHEN "110", ‘Z’ WHEN OTHERS; END behavioral;

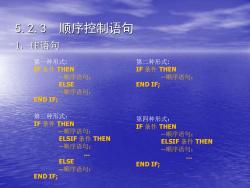

5.2.3 顺序控制语句 1,IF语句 第一种形式: 第二种形式: IF条件THEN IF条件THEN 一顺序语句: 一顺序语句: ELSE END IF; 一顺序语句 END IF; 第三种形式: 第四种形式: IF条件THEN IF条件THEN 一顺序语句: -顺序语句; ELSIF条件THEN ELSIF条件THEN 顺序语句: -顺序语句 ELSE END IF; 顺序语句: END IF;

5.2.3 顺序控制语句 1. IF语句 第一种形式: IF 条件 THEN --顺序语句; ELSE --顺序语句; END IF; 第二种形式: IF 条件 THEN --顺序语句; END IF; 第三种形式: IF 条件 THEN --顺序语句; ELSIF 条件 THEN --顺序语句; … ELSE --顺序语句; END IF; 第四种形式: IF 条件 THEN --顺序语句; ELSIF 条件 THEN --顺序语句; … END IF;

按次数下载不扣除下载券;

注册用户24小时内重复下载只扣除一次;

顺序:VIP每日次数-->可用次数-->下载券;

- 广东海洋大学:《VHDL程序设计语言》课程教学资源(PPT课件)第4章 VHDL编程基础.ppt

- 广东海洋大学:《VHDL程序设计语言》课程教学资源(PPT课件)第3章 集成开发平台QuartusII操作基础.ppt

- 广东海洋大学:《VHDL程序设计语言》课程教学资源(PPT课件)第2章 可编程逻辑器件.ppt

- 广东海洋大学:《VHDL程序设计语言》课程教学资源(PPT课件)第1章 概述.ppt

- 广东海洋大学:《VHDL程序设计语言》课程教学资源(PPT课件)前言(负责人:张健).ppt

- 广东海洋大学:《VHDL程序设计语言》课程教学资源(实验指导)实验十 An Enhanced Processor.pdf

- 广东海洋大学:《VHDL程序设计语言》课程教学资源(实验指导)实验九 A Simple Processor.pdf

- 广东海洋大学:《VHDL程序设计语言》课程教学资源(实验指导)实验八 Memory Blocks.pdf

- 广东海洋大学:《VHDL程序设计语言》课程教学资源(实验指导)实验七 Finite State Machines.pdf

- 广东海洋大学:《VHDL程序设计语言》课程教学资源(实验指导)实验六 Adders, Subtractors, and Multipliers.pdf

- 广东海洋大学:《VHDL程序设计语言》课程教学资源(实验指导)实验五 Clocks and Timers.pdf

- 广东海洋大学:《VHDL程序设计语言》课程教学资源(实验指导)实验四 Counters.pdf

- 广东海洋大学:《VHDL程序设计语言》课程教学资源(实验指导)实验三 Latches, Flip-flops, and Registers.pdf

- 广东海洋大学:《VHDL程序设计语言》课程教学资源(实验指导)实验二 Numbers and Displays.pdf

- 广东海洋大学:《VHDL程序设计语言》课程教学资源(实验指导)实验一 Switches, Lights, and Multiplexers.pdf

- 中国科学技术大学:《计算机图形学》课程教学资源(讲义)第六章 观察(主讲:黄章进).pdf

- 中国科学技术大学:《计算机图形学》课程教学资源(讲义)第四章 输入与交互.pdf

- 中国科学技术大学:《计算机图形学》课程教学资源(讲义)第五章 几何对象与变换.pdf

- 中国科学技术大学:《计算机图形学》课程教学资源(讲义)第二章 计算机图形系统.pdf

- 中国科学技术大学:《计算机图形学》课程教学资源(讲义)第三章 OpenGL编程.pdf

- 广东海洋大学:《VHDL程序设计语言》课程教学资源(PPT课件)第6章 VHDL设计共享.ppt

- 广东海洋大学:《VHDL程序设计语言》课程教学资源(PPT课件)第7章 基本逻辑电路设计.ppt

- 广东海洋大学:《VHDL程序设计语言》课程教学资源(PPT课件)第8章 有限状态机的VHDL设计.ppt

- 广东海洋大学:《VHDL程序设计语言》课程教学资源(PPT课件)第10章 EDA设计的仿真与测试.ppt

- 西安电子科技大学:《计算机网络 Computer Networks》课程教学资源(PPT课件讲稿)第二章 物理层.pptx

- 西安电子科技大学:《计算机网络 Computer Networks》课程教学资源(PPT课件讲稿)第三章 数据链路层.pptx

- 西安电子科技大学:《计算机网络 Computer Networks》课程教学资源(PPT课件讲稿)第四章 网络层.pptx

- 上饶师范学院:《数据库系统原理》课程教学资源(试卷习题)数据库系统原理模拟试卷(考试模拟试题,共十套,含参考答案).doc

- 上饶师范学院:《数据库系统原理》课程教学资源(资料讲义)数据库系统原理总复习(负责人:颜清).doc

- 上饶师范学院:《数据库系统原理》课程教学资源(试卷习题)数据库系统原理习题集及答案.doc

- 上饶师范学院:《数据库系统原理》课程教学资源(资料讲义)数据库系统原理实验讲义(上机实验讲义).doc

- 上饶师范学院:《数据库系统原理》课程教学资源(电子教案)数据库系统原理电子教案(共九章).doc

- 上饶师范学院:《数据库系统原理》课程教学资源(PPT课件)数据库系统概论 An Introducation to Database System(完整版).ppt

- The Not So Short Introduction to LaTeX2ε(Or LATEX 2ε in 139 minutes).pdf

- 同济大学:《大学计算机基础》课程教学资源(试卷习题)试卷样本及答案.doc

- 同济大学:《大学计算机基础》课程教学资源(教案讲义)Data Representation.ppt

- 同济大学:《大学计算机基础》课程教学资源(教案讲义)Basics of Computer System.ppt

- 同济大学:《大学计算机基础》课程教学资源(教案讲义)Database.ppt

- 同济大学:《大学计算机基础》课程教学资源(教案讲义)Microsoft Excel.ppt

- 同济大学:《大学计算机基础》课程教学资源(教案讲义)Fundamentals of Computers Introduction(负责人:臧笛).ppt