中国科学技术大学:《超大规模集成电路设计(VLSI)》课程教学资源(课件讲稿)第9章 CMOS逻辑电路的高级技术

中国绅学我术大学 University of Science and Technology of China 第9章CMOS逻辑电路的高级技术 本章目录 9.1镜像电路 92准nMOS电路 9.3三态电路 9.4时钟控制CMOS 9.5动态CMOS逻辑电路 9.6双轨逻辑电路 2018-9-5 第9章CMOS逻辑电路的高级技术 §91镜像电路 ·对NMOS和PMOS采用相同的拓扑连接。 1异或门(XOR) a⊕b=a,b+a.b a b a⊕b On devices 0 0 0 一nFET ●a⊕b 0 pFET b 0 pFET 1 1 0 nFET Figure 9.1 XOR function table 2018-9-5 第9章CMOS逻辑电路的高级技术 2

2018-9-5 第9章 CMOS逻辑电路的高级技术 1 第 9 章 CMOS逻辑电路的高级技术 逻辑电路的高级技术 本章目录 •9.1 镜像电路 •9.2 准nMOS电路 •9.3 三态电路 •9.4 时钟控制CMOS •9.5 动态CMOS逻辑电路 •9.6 双轨逻辑电路 2018-9-5 第9章 CMOS逻辑电路的高级技术 2 §9.1 镜像电路 • 对NMOS和PMOS采用相同的拓扑连接。 1 异或门(XOR) a ⊕b = a ⋅b + a ⋅b

§9.1镜像电路 镜像XOR电路优点之一:对称的版图 VpD VDD 0.1)(1,04 a ●a⊕b 0.0)(1.1 a b Gnd (a)Circuit (b)Layout Figure 9.2 XOR mirror circuit 2018-9-5 第9章CMOS逻辑电路的高级技术 §9.1镜像电路 镜像XOR电路优点之二: 速度较快 VpD R 9 Rp Cp o.)的 (1.0) o,0内 1,1) Cout Rn R三 Cn Figure 9.3 Switch model for transient calculations 应用Elmore公式:上升时间常数t,=2R,Com+R,Cp 2018-9-5 第9章CMOS逻辑电路的高级技术

2018-9-5 第9章 CMOS逻辑电路的高级技术 3 §9.1 镜像电路 镜像XOR电路优点之一:对称的版图 2018-9-5 第9章 CMOS逻辑电路的高级技术 4 §9.1 镜像电路 镜像XOR电路优点之二:速度较快 Elmore r = 2RpCout + RpCp 应用 公式:上升时间常数τ

§9.1镜像电路 2镜像电路XNOR异或非(同或)门实现: VDD 1,10 (0.0 6 O●b a b a⊕b a⊕b 0 0 0 0 0 1 1 1 0,1) 1,0 Figure 9.4 Exclusive-NOR(XNOR)mirror circuit 2018-9-5 第9章CMOS逻辑电路的高级技术 §9.2准nMOS逻辑 1结构 优点: 晶体管较少,N个输 入的门电路仅需N+1 VpD 个MOS管 VSGP Pull-up Load f ·缺点: nFET (1)静态功耗不为0; ● Logic Pull-down Array (2)是有比逻辑电路 (输出与尺寸有关) Figure 9.5 General structure of a pseudo-nMOS logic gate 2018-9-5 第9章CMOS逻辑电路的高级技术

2018-9-5 第9章 CMOS逻辑电路的高级技术 5 §9.1 镜像电路 2 镜像电路XNOR异或非(同或)门实现: 2018-9-5 第9章 CMOS逻辑电路的高级技术 6 §9.2 准nMOS逻辑 1 结构 • 优点: 晶体管较少,N个输 入的门电路仅需N+1 个MOS管 • 缺点: (1)静态功耗不为0; (2)是有比逻辑电路 (输 出与尺寸有关)

§9.2准nMOS逻辑 2准nMOS逻辑INV VpD VpD B MOSFET尺寸的确定: Dp 设Vm=Voo'且Vou很小; 则pFET工作在饱和区, VOL nFET工作在线性区 Figure 9.6 Pseudo-nMOS inverter la=l→号2Wo-k.Ma-哈]-gUo-1y,2 2 sa=o-a)w--g。. 2018-9-5 第9章CMOS逻辑电路的高级技术 §9.2准nMOS逻辑 例9.1一个CMOS工艺,'oo=5V,'m=0.7V,'p=-0.8V, kn=150uA/V2,k,=68μA/W2。一个准nMOS反相器的尺寸为 (W1L)n=4及(W1L)p=6,这个反相器的输出电压为 a=w-心o-r-台o-nD B =4.3- 4.32-408x4.2=1.75V2 600 如果nMOS反相器的尺寸为(W/L)n=8及(W/L)p=2,则 'o=4.3- 4.32、 136 ×4.22=0.24V 1200 2018-9-5 第9章CMOS逻辑电路的高级技术 8

2018-9-5 第9章 CMOS逻辑电路的高级技术 7 §9.2 准nMOS逻辑 2 准nMOS逻辑 INV • MOSFET尺寸的确定: 设Vin=VDD,且VOL很小; 则pFET工作在饱和区, nFET工作在线性区 2 2 ( | |) 2 [2( ) ] 2 DD Tp p DD Tn OL OL n ⇒ V −V V −V = V − V β β 2 2 ( ) ( ) ( | |) DD Tp n p ⇒VOL = VDD −VTn − VDD −VTn − V − V β β Dn Dp I = I 2018-9-5 第9章 CMOS逻辑电路的高级技术 8 §9.2 准nMOS逻辑 及 ,这个反相器的输出电压为 。一个准 反相器的尺寸为 例 一个 工艺, ( / ) 4 ( / ) 6 150μA/V , 68μA/V nMOS 9.1 CMOS 5V, 0.7V, 0.8V, ' 2 ' 2 = = = = = = = − n p n p DD Tn Tp W L W L k k V V V 4.2 1.75V 600 408 4.3 4.3 ( ) ( ) ( | |) 2 2 2 2 = − − × = = − − − − DD − Tp n p VOL VDD VTn VDD VTn V V β β 如果nMOS反相器的尺寸为(W / L)n = 8及(W / L) p = 2,则 4.2 0.24V 1200 136 4.3 4.32 2 VOL = − − × = ?

§9.2准nMOS逻辑 3准nMOS逻辑NOR和NAND VDD ●a.b ●a+b … a (a)NOR2 gate (b)NAND2 gate Figure 9.7 Pseudo-nMOS NOR and NAND gates 2018-9-5 第9章CMOS逻辑电路的高级技术 §9.2准nMOS逻辑 4准nMOS逻辑AO:f=ab+cd VDD VDD a⊕b a 2 a b b a Gnd (a)General circuit (b)Layout example Figure 9.8 AOI gate in pseudo-nMOS logic 2018-9-5 第9章CMOS逻辑电路的高级技术 10

2018-9-5 第9章 CMOS逻辑电路的高级技术 9 §9.2 准nMOS逻辑 3 准nMOS逻辑 NOR和NAND 2018-9-5 第9章 CMOS逻辑电路的高级技术 10 §9.2 准nMOS逻辑 4 准nMOS 逻辑AOI: f = ab + cd

§9.2准nMOS逻辑 e 准nMOS逻辑的设计特点: (1)适合以NOR为基础的结构 (2)为得到合理的低电平噪声容限,Vo应当小 (3)为减小静态功耗,PMOS沟道电阻应当大 (4)为减小上升时间,PMOS沟道电阻应当小 条件(3)与(4)是矛盾的,可见:实现一个较快的门 意味着较多的静态功耗和较小的噪声容限 (5)适用于对面积要求严格,而性能要求不高的场合 2018-9-5 第9章CMOS逻辑电路的高级技术 §9.3 三态电路 三态电路(隔离总线):H,L,Z(高阻) VpD En Mp Data● En●- En● M2 En f 0 Z Data● 1 Data (a)Symbol and operation (b)CMOS circuit Figure 9.9 Tri-state inverter 2018-9-5 第9章CMOS逻辑电路的高级技术 12

2018-9-5 第9章 CMOS逻辑电路的高级技术 11 §9.2 准nMOS逻辑 准nMOS逻辑的设计特点: (1)适合以NOR为基础的结构 (2)为得到合理的低电平噪声容限,VOL应当小 (3)为减小静态功耗,PMOS沟道电阻应当大 (4)为减小上升时间,PMOS沟道电阻应当小 条件(3)与(4)是矛盾的,可见:实现一个较快的门 意味着较多的静态功耗和较小的噪声容限 (5)适用于对面积要求严格,而性能要求不高的场合 2018-9-5 第9章 CMOS逻辑电路的高级技术 12 §9.3 三态电路 三态电路(隔离总线):H,L,Z(高阻)

§9.3 三态电路 三态反相器的版图 VpD VDD MP En En● M2 Data En Data Mn Gnd Figure 9.10 Tri-state layout 2018-9-5 第9章CMOS逻辑电路的高级技术 13 §9.4时钟控制CMOS 1基本结构 VpD b·pFETs Inputs valid ·f(a,b,c) M2 Cout Vout Hi-Z Hi b nFETs Figure 9.12 Structure of a C2MOS gate 2018-9-5 第9章CMOS逻辑电路的高级技术 14

2018-9-5 第9章 CMOS逻辑电路的高级技术 13 §9.3 三态电路 三态反相器的版图 2018-9-5 第9章 CMOS逻辑电路的高级技术 14 §9.4 时钟控制CMOS 1 基本结构

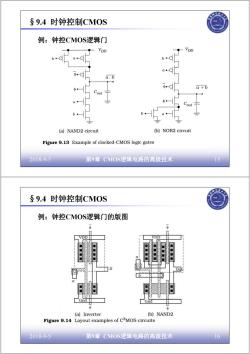

§9.4时钟控制CMOS 例:钟控CMOS逻辑门 VDD DD a·b a+b (a)NAND2 circuit (b)NOR2 circuit Figure 9.13 Example of clocked-CMOS logic gates 2018-9-5 第9章CMOS逻辑电路的高级技术 15 §9.4时钟控制CMOS 例:钟控CMOS逻辑门的版图 VDD VDD ● : a Gnd. Gnd (a)Inverter (b)NAND2 Figure 9.14 Layout examples of C2MOS circuits 2018-9-5 第9章CMOS逻辑电路的高级技术 16

2018-9-5 第9章 CMOS逻辑电路的高级技术 15 §9.4 时钟控制CMOS 例:钟控CMOS逻辑门 2018-9-5 第9章 CMOS逻辑电路的高级技术 16 §9.4 时钟控制CMOS 例:钟控CMOS逻辑门的版图

§9.4时钟控制CMOS 2电荷泄露 ()PN结反向电流 OFF VDD =1d-inWell.connection. v(t) D+ iout 9=0 CoutT V(t) p-substrate 0 connection th (a)Bulk leakage currents (b)Logic 1 voltage decay Figure 9.15 Charge leakage problem 2018-9-5 第9章CMOS逻辑电路的高级技术 17 §9.4时钟控制CMOS dy fou =in-lp=-Cow dt V(t=0)=Vi,in >ip,iou =IL ..=-Cow dt ["ar-ur 为常数0-化} 设最小允许的逻辑1电压为V,则V对应的时间为维持时间1h 电荷泄漏现象使CMOS电路中的最小时钟频率受到限制 2018-9-5 第9章CMOS逻辑电路的高级技术 18

2018-9-5 第9章 CMOS逻辑电路的高级技术 17 §9.4 时钟控制CMOS 2 电荷泄露 (1) PN结反向电流 2018-9-5 第9章 CMOS逻辑电路的高级技术 18 §9.4 时钟控制CMOS t V iout in ip Cout d d = − = − n p out L V (t = 0) =V ,i > i ,i = I 设 1 t V I L Cout d d ∴ = − t C I I V t V out L L ⎟ ⎟ ⎠ ⎞ ⎜ ⎜ ⎝ ⎛ 设 为常数, ( ) = 1 − t C I V V t V t out L d d ( ) ∫ ∫ 1 0 ⎟ ⎟ ⎠ ⎞ ⎜ ⎜ ⎝ ⎛ = − x x h 设最小允许的逻辑 1电压为V ,则V 对应的时间为维持时间 t h x out L h t V C I V t V = ⎟ ⎟ ⎠ ⎞ ⎜ ⎜ ⎝ ⎛ ( ) = 1 − ( ) 1 x L out h V V I C t − ⎟ ⎟ ⎠ ⎞ ⎜ ⎜ ⎝ ⎛ = 电荷泄漏现象使C2MOS电路中的最小时钟频率受到限制

§9.4时钟控制CMOS (2)亚阈值电流Ib:栅源电压小于阈值电压时的漏极电流。 (VGs-Vr)/(nYa) 其中Ioo=Ipo(Vs),Vh=kT/q 亚阈值斜率S:漏极电流减小一个数量级所需栅电压的变化量 S= dVas S=(lnl0)n'h≈2.3n'h d(IgI) 典型值:S=60mV~100mV 3改进方案 改进制造工艺来减少漏电 >开发新类型的晶体管 2018-9-5 第9章CMOS逻辑电路的高级技术 19 §9.5动态CMOS逻辑电路 19 1结构 VDD Mp a nFETs Precharge Evaluate Precharge Mp on Mp off Mp on Mn off Mn on Mn off 0 i T Figure 9.17 Basic dynamic logic gate 两个工作阶段:预充电:=0 求值:1 2018-9-5 第9章CMOS逻辑电路的高级技术 20

2018-9-5 第9章 CMOS逻辑电路的高级技术 19 §9.4 时钟控制CMOS (2) 亚阈值电流Isub:栅源电压小于阈值电压时的漏极电流。 3 改进方案 ¾ 改进制造工艺来减少漏电 ¾ 开发新类型的晶体管 e I I V V kT q L W I I D D DS th V V nV D D GS T th ⎟ = = ⎠ ⎞ ⎜ ⎝ ⎛ = 0 ( − ) ( ) 其中 0 0 ( ), S nVth 3nVth = (ln10) ≈ 2. d(lg ) d D GS I V S = 亚阈值斜率S:漏极电流减小一个数量级所需栅电压的变化量 典型值:S = 60mV ~ 100mV 2018-9-5 第9章 CMOS逻辑电路的高级技术 20 §9.5 动态CMOS逻辑电路 1 结构 两个工作阶段:预充电:φ=0 求值:φ=1

按次数下载不扣除下载券;

注册用户24小时内重复下载只扣除一次;

顺序:VIP每日次数-->可用次数-->下载券;

- 中国科学技术大学:《超大规模集成电路设计(VLSI)》课程教学资源(课件讲稿)第8章 高速CMOS逻辑电路设计.pdf

- 中国科学技术大学:《超大规模集成电路设计(VLSI)》课程教学资源(课件讲稿)第7章 CMOS逻辑门电子学分析.pdf

- 中国科学技术大学:《超大规模集成电路设计(VLSI)》课程教学资源(课件讲稿)第6章 MOSFET的电气特性.pdf

- 中国科学技术大学:《超大规模集成电路设计(VLSI)》课程教学资源(课件讲稿)第5章 物理设计的基本要素.pdf

- 中国科学技术大学:《超大规模集成电路设计(VLSI)》课程教学资源(课件讲稿)第4章 CMOS集成电路的制造.pdf

- 中国科学技术大学:《超大规模集成电路设计(VLSI)》课程教学资源(课件讲稿)第3章 CMOS集成电路的物理结构.pdf

- 中国科学技术大学:《超大规模集成电路设计(VLSI)》课程教学资源(课件讲稿)第2章 MOSFET逻辑设计.pdf

- 中国科学技术大学:《超大规模集成电路设计(VLSI)》课程教学资源(课件讲稿)第1章 VLSI概论(主讲:胡新伟).pdf

- 《超大规模集成电路设计(VLSI)》课程教学资源(书籍教材)超大规模集成电路与系统导论 Introduction to VLSI Circuits and Systems(共十六章).pdf

- 中国科学技术大学:《超大规模集成电路设计(VLSI)》课程教学资源(设计实验)Cadence IC 设计实验(Diva Interactive Verification).pdf

- 山东大学:《DSP原理与应用》课程教学资源(PPT课件讲稿,2014)第7章 TMS320C54x片内外设及其应用.pptx

- 山东大学:《DSP原理与应用》课程教学资源(PPT课件讲稿,2014)第9章 TMS320C54x硬件设计及接口技术.pptx

- 山东大学:《DSP原理与应用》课程教学资源(PPT课件讲稿,2014)第8章 数字信号处理典型算法程序设计.pptx

- 山东大学:《DSP原理与应用》课程教学资源(PPT课件讲稿,2014)第6章 TMS320C54x软件开发环境.pptx

- 山东大学:《DSP原理与应用》课程教学资源(PPT课件讲稿,2014)第5章 C54x高级C语言程序设计.pptx

- 山东大学:《DSP原理与应用》课程教学资源(PPT课件讲稿,2014)第4章 汇编语言程序设计.pptx

- 山东大学:《DSP原理与应用》课程教学资源(PPT课件讲稿,2014)第3章 汇编语言指令系统.pptx

- 山东大学:《DSP原理与应用》课程教学资源(PPT课件讲稿,2014)第2章 TMS320C54x的硬件结构及原理.pptx

- 山东大学:《DSP原理与应用》课程教学资源(PPT课件讲稿,2014)第1章 DSP技术概要(主讲:刘忠国).pptx

- 聊城大学:《信息与系统》课程教学资源(课件讲稿)第八章 离散时间系统的z域分析.pdf

- 中国科学技术大学:《超大规模集成电路设计(VLSI)》课程教学资源(课件讲稿)第11章 常用的VLSI系统部件.pdf

- 中国科学技术大学:《超大规模集成电路设计(VLSI)》课程教学资源(课件讲稿)第12章 CMOS VLSI运算电路.pdf

- 中国科学技术大学:《数字逻辑电路》课程教学资源(实验课件)数字逻辑电路实验讲义(图片版).pdf

- 中国科学技术大学:《数字逻辑电路》课程教学资源(实验课件)数字钟.pdf

- 中国科学技术大学:《数字逻辑电路》课程教学资源(实验课件)移位寄存器.pdf

- 中国科学技术大学:《数字逻辑电路》课程教学资源(实验课件)数据选择器.pdf

- 中国科学技术大学:《数字逻辑电路》课程教学资源(实验课件)全加器实验.pdf

- 中国科学技术大学:《数字逻辑电路》课程教学资源(实验课件)抢答器.pdf

- 中国科学技术大学:《数字逻辑电路》课程教学资源(实验课件)计数器及其应用——电子秒表.pdf

- 中国科学技术大学:《数字逻辑电路》课程教学资源(实验课件)编码器和译码器.pdf

- 中国科学技术大学:《数字逻辑电路》课程教学资源(课件讲稿)绪论(主讲:胡新伟).pdf

- 中国科学技术大学:《数字逻辑电路》课程教学资源(课件讲稿)第一章 数制和码制.pdf

- 中国科学技术大学:《数字逻辑电路》课程教学资源(课件讲稿)第二章 逻辑代数基础.pdf

- 中国科学技术大学:《数字逻辑电路》课程教学资源(课件讲稿)第三章 门电路.pdf

- 中国科学技术大学:《数字逻辑电路》课程教学资源(课件讲稿)第四章 组合逻辑电路.pdf

- 中国科学技术大学:《数字逻辑电路》课程教学资源(课件讲稿)第五章 半导体存储电路.pdf

- 中国科学技术大学:《数字逻辑电路》课程教学资源(课件讲稿)第六章 时序逻辑电路.pdf

- 中国科学技术大学:《数字逻辑电路》课程教学资源(课件讲稿)第七章 脉冲波形的产生和整形电路.pdf

- 合肥工业大学:《数字电子技术基础》课程教学资源(课件讲稿)序言(主讲:梁华国、黄正峰).pdf

- 合肥工业大学:《数字电子技术基础》课程教学资源(课件讲稿)第一章 数制与编码(不同数制间的转换).pdf