广东海洋大学:《数字电子技术》课程教学资源(PPT课件)第8章 可编程逻辑器件

第八章 可编程逻辑器件 8.1可编程逻辑器件的基本特点 数字集成电路从功能上可分为通用型、专用 型两大类。 利用通用芯片设计复杂数字电路时:线路连 线多,使电路的可靠性下降;修改的工作量大; 保密性差。 专用芯片的优点:体积小、功耗低、可靠性 高。缺点:设计制作周期长、成本高

第八章 可编程逻辑器件 8.1 可编程逻辑器件的基本特点 数字集成电路从功能上可分为通用型、专用 型两大类。 利用通用芯片设计复杂数字电路时:线路连 线多,使电路的可靠性下降;修改的工作量大; 保密性差。 专用芯片的优点:体积小、功耗低、可靠性 高。缺点:设计制作周期长、成本高

PLD的特点:是一种按通用器件来生产,但 逻辑功能是由用户通过对器件编程来设定的集成电 路。 一个PLD芯片中集成了大量的基本逻辑单元 和可编程的连接元件。通过对这些连接元件的编程, 就可以方便地设计出具有各种不同逻辑功能的专用 集成电路。 优点:成本低、设计周期短、修改方便等

PLD的特点:是一种按通用器件来生产,但 逻辑功能是由用户通过对器件编程来设定的集成电 路。 一个PLD芯片中集成了大量的基本逻辑单元 和可编程的连接元件。通过对这些连接元件的编程, 就可以方便地设计出具有各种不同逻辑功能的专用 集成电路。 优点:成本低、设计周期短、修改方便等

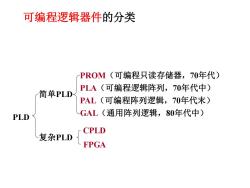

可编程逻辑器件的分类 PROM(可编程只读存储器,70年代) PLA(可编程逻辑阵列,70年代中) 简单PLD PAL(可编程阵列逻辑,70年代末) PLD GAL(通用阵列逻辑,80年代中) CPLD 复杂PLD FPGA

PLD 简单PLD PROM(可编程只读存储器,70年代) PLA(可编程逻辑阵列,70年代中) PAL(可编程阵列逻辑,70年代末) GAL(通用阵列逻辑,80年代中) 复杂PLD CPLD FPGA 可编程逻辑器件的分类

8.2可编程逻辑阵列(PLA) 电路结构: 一个可编程的与逻辑阵列、一个可编程的或逻辑 阵列、输入缓冲电路和输出缓冲电路。 输 可编程 输 入缓冲电 与逻辑 阵列 输 可编程 Yo 或逻辑 阵列 入缓冲电 : 籀 Ym-1 EN

8.2 可编程逻辑阵列(PLA) 电路结构: 一个可编程的与逻辑阵列、一个可编程的或逻辑 阵列、输入缓冲电路和输出缓冲电路

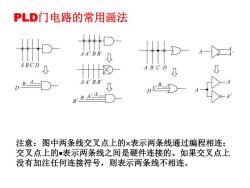

PLD门电路的常用画法 AABB D ABCD D B A AA'BB D 注意:图中两条线交叉点上的×表示两条线通过编程相连: 交叉点上的表示两条线之间是硬件连接的。如果交叉点上 没有加注任何连接符号,则表示两条线不相连

PLD门电路的常用画法 注意:图中两条线交叉点上的表示两条线通过编程相连; 交叉点上的•表示两条线之间是硬件连接的。如果交叉点上 没有加注任何连接符号,则表示两条线不相连

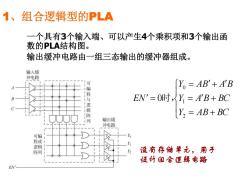

1、组合逻辑型的PLA 一个具有3个输入端、可以产生4个乘积项和3个输出函 数的PLA结构图。 输出缓冲电路由一组三态输出的缓冲器组成。 输入缓 冲电路 可 Yo=AB'+A'B 程与逻 EN'=O时,Y=A'B+BC Y,=AB+BC 列 输出缓 冲电路 可编 程或 Y 逻辑 阵列 没有存储单元,用子 设外组合逻辑电路 EN

1、组合逻辑型的PLA 一个具有3个输入端、可以产生4个乘积项和3个输出函 数的PLA结构图。 输出缓冲电路由一组三态输出的缓冲器组成。 = + = + = + = Y AB BC Y A B BC Y AB A B EN 2 1 0 0时, 没有存储单元,用于 设计组合逻辑电路

2、时序逻辑型PLA电路 缓冲电路中增加了若干触发器 将这些触发器的状态反馈到可编程的与逻辑阵列上 CLK EN

2、时序逻辑型PLA电路 缓冲电路中增加了若干触发器 将这些触发器的状态反馈到可编程的与逻辑阵列上

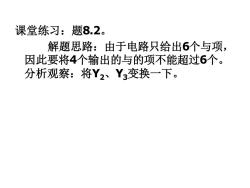

课堂练习:题8.2。 解题思路:由于电路只给出6个与项, 因此要将4个输出的与的项不能超过6个。 分析观察:将Y2、Y3变换一下

课堂练习:题8.2。 解题思路:由于电路只给出6个与项, 因此要将4个输出的与的项不能超过6个。 分析观察:将Y2、Y3变换一下

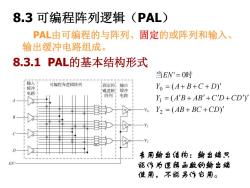

8.3可编程阵列逻辑(PAL) PAL由可编程的与阵列、固定的或阵列和输入、 输出缓冲电路组成。 8.3.1PAL的基本结构形式 当EN'=O时 输入 可编程与逻辑阵列 固定的输出 缓冲 Yo=(4+B+C+D)' 或逻辑!缓冲 电路 阵列 电路 Y=(4'B+AB'+C'D+CD) Yo Y2=(AB+BC+CD) 专用输出结构:输出瑞只 能作为逻辑函数的输出瑞 使用,不能另作它用

8.3 可编程阵列逻辑(PAL) PAL由可编程的与阵列、固定的或阵列和输入、 输出缓冲电路组成。 8.3.1 PAL的基本结构形式 ( ) ( ) ( ) ' 0 2 1 0 = + + = + + + = + + + = Y AB BC CD Y A B AB C D CD Y A B C D 当EN 时 专用输出结构:输出端只 能作为逻辑函数的输出端 使用,不能另作它用

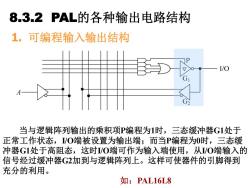

83.2PAL的各种输出电路结构 1.可编程输入输出结构 当与逻辑阵列输出的乘积项P编程为1时,三态缓冲器G1处于 正常工作状态,/O端被设置为输出端;而当P编程为0时,三态缓 冲器G1处于高阻态,这时/O端可作为输入端使用,从/O端输入的 信号经过缓冲器G2加到与逻辑阵列上。这样可使器件的引脚得到 充分的利用。 如:PAL16L8

1. 可编程输入输出结构 8.3.2 PAL的各种输出电路结构 当与逻辑阵列输出的乘积项P编程为1时,三态缓冲器G1处于 正常工作状态,I/O端被设置为输出端;而当P编程为0时,三态缓 冲器G1处于高阻态,这时I/O端可作为输入端使用,从I/O端输入的 信号经过缓冲器G2加到与逻辑阵列上。这样可使器件的引脚得到 充分的利用。 如:PAL16L8

按次数下载不扣除下载券;

注册用户24小时内重复下载只扣除一次;

顺序:VIP每日次数-->可用次数-->下载券;

- 广东海洋大学:《数字电子技术》课程教学资源(PPT课件)7.2.2 可编程ROM 7.2.3 可擦除的可编程ROM 7.2.4 利用ROM实现组合逻辑函数 7.3 随机存取存储器(RAM)7.4.2 字扩展方式.ppt

- 广东海洋大学:《数字电子技术》课程教学资源(PPT课件)10.3.3 逐次渐近型A/D转换器 10.3.5 A/D转换器的主要技术指标.ppt

- 广东海洋大学:《数字电子技术》课程教学资源(PPT课件)第10章 模数与数模转换 10.2 D/A转换器 10.3.1 A/D转换的一般工作过程.ppt

- 广东海洋大学:《数字电子技术》课程教学资源(PPT课件)9.5 555定时器.ppt

- 广东海洋大学:《数字电子技术》课程教学资源(PPT课件)9.3 单稳态电路 9.4 多谐振荡电路 9.4.1 对称式和非对称式多谐振荡电路 9.4.2 环形振荡电路 9.4.3 利用施密特触发电路构成的多谐振荡电路.ppt

- 广东海洋大学:《数字电子技术》课程教学资源(PPT课件)6.4.1 简单同步时序逻辑电路的设计 6.4.2 复杂时序逻辑电路的设计 6.5 时序逻辑电路中的竞争—冒险现象.ppt

- 广东海洋大学:《数字电子技术》课程教学资源(PPT课件)熟练掌握用MSI计数器(74163、74160)实现N进制计数器的方法.ppt

- 广东海洋大学:《数字电子技术》课程教学资源(PPT课件)4.2 常用的组合逻辑电路 4.2.1 译码器.ppt

- 广东海洋大学:《数字电子技术》课程教学资源(PPT课件)4.1 组合逻辑电路的特点和分析方法 4.1.2 组合逻辑电路的分析方法 4.2 常用的组合逻辑电路 4.2.2 编码器.ppt

- 广东海洋大学:《数字电子技术》课程教学资源(PPT课件)3.4 TTL门电路 3.4.2 TTL与非门、或非门、与或非门和异或门 3.4.3 三态输出和集电极开路输出的TTL门电路 3.4.4 TTL门电路的电气特性和参数.ppt

- 广东海洋大学:《数字电子技术》课程教学资源(PPT课件)6.3.3 计数器.ppt

- 广东海洋大学:《数字电子技术》课程教学资源(PPT课件)6.3.1 寄存器 6.3.2 移位寄存器.ppt

- 广东海洋大学:《数字电子技术》课程教学资源(PPT课件)5.4 时钟边沿触发的触发器 5.5 触发器逻辑功能的分类及逻辑功能的描述.ppt

- 广东海洋大学:《数字电子技术》课程教学资源(PPT课件)掌握电平触发器、脉冲触发器各自的动作特点及波形绘制.ppt

- 广东海洋大学:《数字电子技术》课程教学资源(PPT课件)掌握组合逻辑电路的设计方法.ppt

- 广东海洋大学:《数字电子技术》课程教学资源(PPT课件)4.2.3 数据选择器 4.2.4 加法器 4.2.5 数值比较器.ppt

- 广东海洋大学:《数字电子技术》课程教学资源(PPT课件)3.2.3 三态输出和漏极开路输出的CMOS门电路 3.2.4 CMOS电路的静电防护和锁定效应 3.2.5 CMOS电路的电气特性和参数 3.3.1 双极型二极管的开关特性和二极管门电路 3.3.2 双极型的三极管的开关特性.ppt

- 广东海洋大学:《数字电子技术》课程教学资源(PPT课件)2.5 具有无关项的逻辑函数及其化简 3.2.1 CMOS反相器和传输门 3.2.2 CMOS与非门、或非门和异或门.ppt

- 广东海洋大学:《数字电子技术》课程教学资源(PPT课件)2.3.7 逻辑函数描述方法间的转换 2.4.2 卡诺图化简法.ppt

- 广东海洋大学:《数字电子技术》课程教学资源(PPT课件)2.3 逻辑函数及其描述方法 2.6 逻辑函数式形式的变换.ppt

- 广东海洋大学:《数字电子技术》课程教学资源(PPT课件)数字电路复习提纲.ppt

- 广东海洋大学:电子工程系《C语言与C++入门》课程教学大纲.pdf

- 广东海洋大学:电子工程系《模拟电路》课程教学大纲.pdf

- 广东海洋大学:电子工程系《电路分析》课程教学大纲.pdf

- 广东海洋大学:电子工程系《信号与系统》课程教学大纲.pdf

- 广东海洋大学:电子工程系《微机原理与应用》课程教学大纲.pdf

- 广东海洋大学:电子工程系《数子电子技术》课程教学大纲.pdf

- 广东海洋大学:电子工程系《单片机》课程教学大纲.pdf

- 广东海洋大学:电子工程系《高频电子线路》课程教学大纲.pdf

- 广东海洋大学:电子工程系《计算机网络技术》课程教学大纲.pdf

- 广东海洋大学:电子工程系《通信原理》课程教学大纲.pdf

- 广东海洋大学:电子工程系《信息与编码》课程教学大纲.pdf

- 广东海洋大学:电子工程系《数字信号处理》课程教学大纲.pdf

- 广东海洋大学:电子工程系《电子测量与智能仪器》课程教学大纲.pdf

- 广东海洋大学:电子工程系《电磁场与电磁波》课程教学大纲.pdf

- 广东海洋大学:电子工程系《信息与编码》课程教学大纲.pdf

- 广东海洋大学:电子工程系《密码学》课程教学大纲.pdf

- 广东海洋大学:电子工程系《移动通信》课程教学大纲.pdf

- 广东海洋大学:电子工程系《程控交换原理》课程教学大纲.pdf

- 广东海洋大学:电子工程系《传感器技术》课程教学大纲.pdf