中国科学技术大学:《计算机组成原理》课程教学资源(课件讲稿,2022)04 RV处理器设计(多周期、微程序)

The Processor Implementation: Datapath Control “Computer Organization&Design” 第四章

The Processor Implementation: Datapath & Control “Computer Organization & Design ” 第四章

内容提要 ● 多周期设计需求:CSC采用 -时钟周期对性能的影响 一复用功能部件,减少硬件开销 ·多周期实现 一数据通路,控制器(状态机,微程序) COD5,RV Edition 2ed,$4.5 ·唐本

内容提要 • 多周期设计需求:CISC采用 – 时钟周期对性能的影响 – 复用功能部件,减少硬件开销 • 多周期实现 – 数据通路,控制器(状态机,微程序) • COD5,RV Edition_2ed,$4.5 • 唐本

指令周期:single-cycle vs.multicycle Single-cycle Implementation:定长指令周期 clock waste waste add sto,st1,st2 beg$t0,$t1,工 Multicycle Implementation:不定长指令周期 clockΠTU add sto,st1,st2 beg$t0,$t1,工 Multicycle Implementation: less waste higher performance

指令周期:single-cycle vs. multicycle • Multicycle Implementation: less waste = higher performance add $t0,$t1,$t2 beq $t0,$t1,L Single-cycle Implementation:定长指令周期 Multicycle Implementation:不定长指令周期 add $t0,$t1,$t2 beq $t0,$t1,L waste waste clock clock

多周期实现(见COD5-RV32ed) ·根据指令执行所使用的功能部件,将执行过程划 分成多个阶段,每个阶段一个时钟周期 一在一个周期内的各个部件并行工作 ·只有控制信号有效的部件作有用功! ·复用:功能部件可以在不同的阶段(周期)使用 一有利于降低硬件实现复杂度和成本 一竞争:结构冲突 一中间结果暂存 Data Register PC Address Instruction Registers Address Instruction Register memory Data Register# memory Data llxx@ustc.edu.cn 4

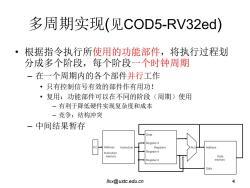

llxx@ustc.edu.cn 4 多周期实现(见COD5-RV32ed) • 根据指令执行所使用的功能部件,将执行过程划 分成多个阶段,每个阶段一个时钟周期 – 在一个周期内的各个部件并行工作 • 只有控制信号有效的部件作有用功! • 复用:功能部件可以在不同的阶段(周期)使用 – 有利于降低硬件实现复杂度和成本 – 竞争:结构冲突 – 中间结果暂存

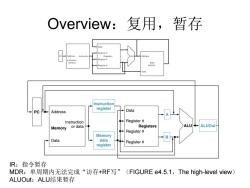

Overview:复用,暂存 Data R8gis时ar# Address Instruction Registers Address nstuuction R8gIs咸8r# memory Data Regis以er# memory Data Instruction register PC Address Data Instruction Register or data Registers ALU ALUOut Memory Register Memory Data data Register register IR:指令暂存 MDR:单周期内无法完成“访存+RF写”(FIGURE e4.5.1,The high-level view) ALUOut:ALU结果暂存

Overview:复用,暂存 IR:指令暂存 MDR:单周期内无法完成“访存+RF写”(FIGURE e4.5.1,The high-level view) ALUOut:ALU结果暂存

五步法第一步 ·时钟周期确定:工作量均衡 一假设一个时钟周期内可以完成 ·一次寄存器读写(2 reads or one write),or ·一次ALU操作,or ·一次MEM访问(IF,W,SW) 1.Instruction 2.Decode/ 3.Execute 4.Memory 5.Reg. Fetch Register Write Read

五步法第一步 • 时钟周期确定:工作量均衡 – 假设一个时钟周期内可以完成 • 一次寄存器读写(2 reads or one write),or • 一次ALU操作,or • 一次MEM访问(IF,lw,sw)

指令执行的阶段划分 1.Instruction 2.Decode/ 3.Execute 4.Memory 5.Reg. Fetch Register Write ·共5个阶段 Read -取指:取指,PC+1 -i 译码:译码阶段、计算beq目标地址 -执行:R-type指令执行、访存地址计算,分支完成阶段 -访存:w读,store和R-type指令完成阶段 -写回:w完成阶段 注意 -指令周期不定长:分别为3、4、5个时钟周期 一时钟周期定长: ·时钟周期标识(状态):控制器据此发出所需控制信号 clk gating llxx@ustc.edu.cn 7

llxx@ustc.edu.cn 7 指令执行的阶段划分 • 共5个阶段 – 取指:取指,PC+1 – 译码:译码阶段、计算beq目标地址 – 执行:R-type指令执行、访存地址计算,分支完成阶段 – 访存:lw读,store和R-type指令完成阶段 – 写回:lw完成阶段 • 注意 – 指令周期不定长:分别为3、4、5个时钟周期 – 时钟周期定长: • 时钟周期标识(状态):控制器据此发出所需控制信号 – clk gating

funct7 rs2 rs1 funct3 rd opcode R-type 多周期数据通路 immediate[11:0] rs1 funct3 rd opcode Itype mmed[11:5] rs2 rs1 funct3 immed[4:0] opcode S-type immed12,10:5] rs2 rs1 funct3 immed[4:1,11] opcode B-type 取指 lw/sw PC+4 PC 0 M Instruction Read 0 U Address [19-15] register 1 M X Read u 1 Instruction data 1 Memory Read [24-20] 1 Zero register 2 MemData Instruction Registers ALU ALU ALUOut [11-7刀 Writ Read result Write register data 2 B 0 data Instruction 1 M register Write u 0 data Instruction M [31-0] X 1 Memory Imm data Gen register beq SW I-type/lw/sw FIGURE e4.5.2 llxx@ustc.edu.cn 8

llxx@ustc.edu.cn 8 多周期数据通路 取指 lw/sw PC+4 I-type/lw/sw beq sw FIGURE e4.5.2

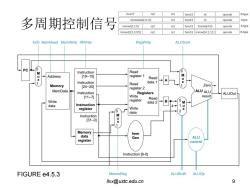

funct7 rs2 rs1 funct3 rd opcode R-type 多周期控制信号 immediate[11:0] rs1 funct3 rd opcode I-type immed(11:5] rs2 rs1 funct3 immed[4:0] opcode S-type immed12,10:5] rs2 rs1 funct3 immed[4:1,11] opcode B-type lorD MemRead MemWrite IRWrite RegWrite ALUSrcA PC 0 Instruction Read 0 M Address [19-15] register 1 M X Read A Instruction Memory Read data 1 [24-20] Zero register 2 MemData Instruction Registers ALU ALU ALUOut [11-7刀 Write result Write register Read data 2 B M data Instruction u register o Write data Instruction M [31-0] 1 Memory Imm data Gen ALU register control Instruction [6-0] FIGURE e4.5.3 MemtoReg ALUSrcB ALUOp llxx@ustc.edu.cn 9

llxx@ustc.edu.cn 9 多周期控制信号 FIGURE e4.5.3

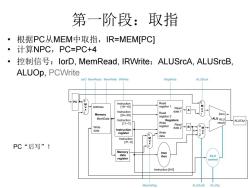

第一阶段:取指 根据PC从MEM中取指,IR=MEM[PC] 计算NPC,PC=PC+4 控制信号:lorD,MemRead,IRWrite;ALUSrcA,ALUSrcB ALUOp,PCWrite orD MemRead MemWrite IRWrite RegWrite ALUSrcA PC 0 Instruction Read Address [19-15 register 1 Read Instruction Read data 1 Memory [24-20] 1 Zero register 2 MemData Instruction Registers ALU ALU ALUOut [11-7刀 Write result Read Write register data 2 M data Instruction register Write data 2 Instruction [31-0 PC“后写”! Memory Imm data Gen ALU register control Instruction [6-0] MemtoReg ALUSrcB ALUOp

10 第一阶段:取指 • 根据PC从MEM中取指,IR=MEM[PC] • 计算NPC,PC=PC+4 • 控制信号:IorD, MemRead, IRWrite;ALUSrcA, ALUSrcB, ALUOp, PCWrite PC“后写”!

按次数下载不扣除下载券;

注册用户24小时内重复下载只扣除一次;

顺序:VIP每日次数-->可用次数-->下载券;

- 中国科学技术大学:《计算机组成原理》课程教学资源(课件讲稿,2022)03 处理器设计(单周期).pdf

- 中国科学技术大学:《计算机组成原理》课程教学资源(课件讲稿,2022)02 指令系统.pdf

- 中国科学技术大学:《计算机组成原理》课程教学资源(课件讲稿,2022)01 概述.pdf

- 中国科学技术大学:《计算机组成原理》课程教学资源(课件讲稿,2022)课程简介(主讲:李曦).pdf

- 中国科学技术大学:《高级操作系统 Advanced Operating System》课程PPT教学课件(分布式系统设计)分布式程序设计(主讲:熊焰).ppt

- 中国科学技术大学:《高级操作系统 Advanced Operating System》课程PPT教学课件(分布式系统设计)分布式进程调度和容错.ppt

- 中国科学技术大学:《高级操作系统 Advanced Operating System》课程PPT教学课件(分布式系统设计)处理机分配算法举例(部分).ppt

- 中国科学技术大学:《高级操作系统 Advanced Operating System》课程PPT教学课件(分布式系统设计)分布式路由算法(3/3).ppt

- 中国科学技术大学:《高级操作系统 Advanced Operating System》课程PPT教学课件(分布式系统设计)分布式路由算法(2/3).ppt

- 中国科学技术大学:《高级操作系统 Advanced Operating System》课程PPT教学课件(分布式系统设计)分布式路由算法(1/3).ppt

- 中国科学技术大学:《安全操作系统》课程教学资源(PPT课件讲稿)第十一讲 国外知名安全操作系统介绍——SELinux CaseStudy SELinux.ppt

- 中国科学技术大学:《安全操作系统》课程教学资源(PPT课件讲稿)第十讲 实验讲解——文件恢复(Linux文件系统和ext2).ppt

- 中国科学技术大学:《安全操作系统》课程教学资源(PPT课件讲稿)第十讲 实验讲解——文件恢复 about experiment file recovery.ppt

- 中国科学技术大学:《安全操作系统》课程教学资源(PPT课件讲稿)第九讲 实验讲解——口令破解 about experiment Password cracking.ppt

- 中国科学技术大学:《安全操作系统》课程教学资源(PPT课件讲稿)第八讲 主流操作系统中的安全技术——Windows GOS Windows Security.ppt

- 中国科学技术大学:《安全操作系统》课程教学资源(PPT课件讲稿)第七讲 安全操作系统的设计与实现 Design Implementation.ppt

- 中国科学技术大学:《安全操作系统》课程教学资源(PPT课件讲稿)第六讲 主流操作系统中的安全技术——Linux GOS Linux Security.ppt

- 中国科学技术大学:《安全操作系统》课程教学资源(PPT课件讲稿)第五讲 渗透测试技术 Penetration testing.ppt

- 中国科学技术大学:《安全操作系统》课程教学资源(PPT课件讲稿)第四讲 操作系统安全体系结构 OSSecurityArch.ppt

- 中国科学技术大学:《安全操作系统》课程教学资源(PPT课件讲稿)第一讲 绪论(主讲:陈香兰).ppt

- 中国科学技术大学:《计算机组成原理》课程教学资源(课件讲稿,2022)05 RV处理器设计——流水线.pdf

- 中国科学技术大学:《计算机组成原理》课程教学资源(课件讲稿,2022)06 RV处理器设计——流水线冲突及冒险.pdf

- 中国科学技术大学:《计算机组成原理》课程教学资源(课件讲稿,2022)07 RV处理器设计(流水线冒险、分支、多发射).pdf

- 中国科学技术大学:《计算机组成原理》课程教学资源(课件讲稿,2022)08 RV处理器设计——异常.pdf

- 中国科学技术大学:《计算机组成原理》课程教学资源(课件讲稿,2022)09 存储器-0(层次存储概述、Cache).pdf

- 中国科学技术大学:《计算机组成原理》课程教学资源(课件讲稿,2022)10 存储器-1(SRAM/DRAM原理、主存系统构建).pdf

- 中国科学技术大学:《计算机组成原理》课程教学资源(课件讲稿,2022)11 存储器-2(外存储器).pdf

- 中国科学技术大学:《计算机组成原理》课程教学资源(课件讲稿,2022)12 存储器-3(虚拟存储器).pdf

- 中国科学技术大学:《计算机组成原理》课程教学资源(课件讲稿,2022)13 存储器-4(存储系统的可靠性——校验、RAID).pdf

- 中国科学技术大学:《计算机组成原理》课程教学资源(课件讲稿,2022)14 系统互连与通信——总线(同步、仲裁).pdf

- 中国科学技术大学:《计算机组成原理》课程教学资源(课件讲稿,2022)15 外设、输入输出系统.pdf

- 中国科学技术大学:《计算机组成原理》课程教学资源(课件讲稿,2023)课程简介.pdf

- 中国科学技术大学:《计算机组成原理》课程教学资源(课件讲稿,2023)01 概述(主讲:李曦).pdf

- 中国科学技术大学:《计算机组成原理》课程教学资源(课件讲稿,2023)02 指令系统.pdf

- 中国科学技术大学:《计算机组成原理》课程教学资源(课件讲稿,2023)03 RV处理器设计——单周期.pdf

- 中国科学技术大学:《计算机组成原理》课程教学资源(课件讲稿,2023)04 RV处理器设计——多周期.pdf

- 中国科学技术大学:《计算机组成原理》课程教学资源(课件讲稿,2023)05 RV处理器设计——流水线.pdf

- 中国科学技术大学:《计算机组成原理》课程教学资源(课件讲稿,2023)06 RV处理器设计——流水线冲突及冒险.pdf

- 中国科学技术大学:《计算机组成原理》课程教学资源(课件讲稿,2023)07 RV处理器设计——流水线冒险、分支、多发射.pdf

- 中国科学技术大学:《计算机组成原理》课程教学资源(课件讲稿,2023)08 RV处理器设计——异常与中断.pdf